Содержание

- 1 Триггер — что это за устройство

- 2 Как работает JK-триггер

- 3 Алгоритм работы

- 4 Как реализованы функции JK-триггера

- 4.1 На J и K нулевые значения

- 4.2 На J и K единичные значения

- 4.3 J и K имеют противоположные значения

- 5 Области применения триггера

- 6 Видео по теме

Существует несколько различных типов триггеров, из которых JK считается наиболее универсальным. JK-триггеры находят применение и как отдельные микросхемы, и в качестве элементов для процессоров. Их использование позволяет создавать схемы, действующие по достаточно сложным алгоритмам.

Триггер — что это за устройство

Он представляет собой электронное устройство, способное на протяжении длительного времени сохранять одно из двух или нескольких состояний. Это происходит до тех пор, пока на него подаётся электропитание. Существует несколько типов триггеров, каждый из которых имеет свою сферу применения. Фактически они являются базовыми элементами. На их основе создаются различные цифровые электронные устройства.

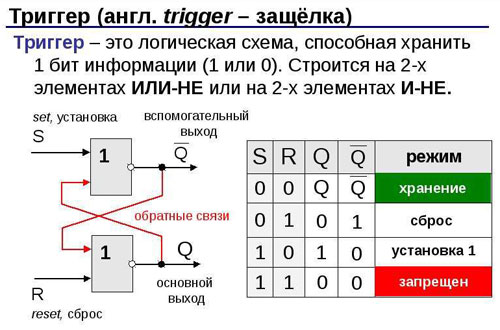

Триггер способен на протяжении довольно длительного промежутка времени пребывать в одном устойчивом режиме из нескольких возможных, а затем под действием входных сигналов переходить из одного режима в другой. Состоит он из элементарных логических элементов, функционирующих по правилам математической логики. Это могут быть ИЛИ-НЕ и И-НЕ. Первые из них функционируют в одноединичном прямом коде, то есть, на выходе одного из элементов будет 1, а на выходах других — 0. Устройство с элементами второго вида работает в однонулевом инверсном коде: на выходе одного из них 0, а на выходах других — 1.

Как работает JK-триггер

Это электронное устройство работает строго по определённому алгоритму, предусматривающему поступление входных значений и обеспечивающему формирование выходных.

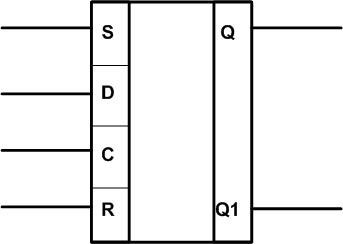

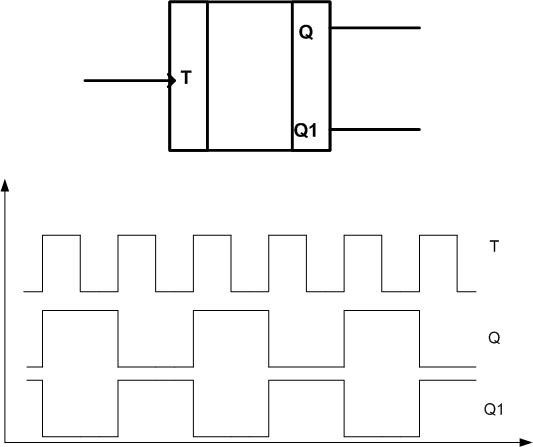

Как видно из схемы, триггер имеет три входа, на которые поступают следующие сигналы:

- J, K — информационные сигналы. Они принимают значение 0 или 1. Каждой комбинации соответствует определённое выходное значение.

- C — двоичный сигнал, который определяет, будут ли меняться выходные сигналы на основании действующего алгоритма или нет. Обычно срабатывание происходит при переходе от единичного к нулевому значению. Также говорят, что срабатывание происходит при отрицательном фронте сигнала.

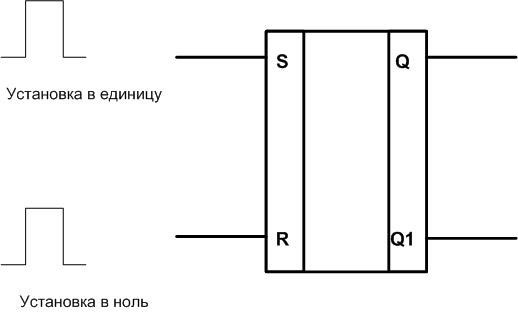

В этой схеме имеется два выхода:

- Q — прямой. Выдает значение, которое на данный момент хранится в триггере.

- Q1 также обозначают как Q с горизонтальной чертой сверху — инверсный. Этот сигнал всегда будет противоположным по отношению к Q.

JK-триггер — это своего рода усовершенствованный RS-триггер. В последнем наблюдается одно запрещённое состояние, использование которого приводит к неопределённому результату на выходе. В JK-устройстве такое состояние исключено. В остальном оба элемента действуют аналогично.

JK-триггер — универсальное устройство. На его базе можно построить простой и асинхронный Т-триггер, D-триггер, синхронный RS-триггер

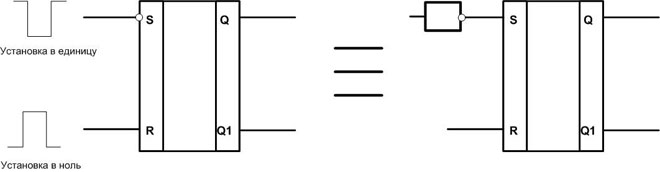

Есть еще комбинированный JK-триггер. От универсального он отличается двумя дополнительными асинхронными входами S и R. Последние позволяют предварительно установить устройство в определенный режим (логического нуля или единицы).

Алгоритм работы

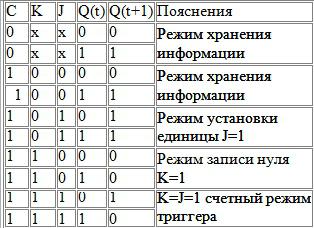

Если на вход C поступает сигнал, равный нулю, то выходные значения будут сохранены. Как только он станет равным единице, формирование значения Q будет происходить по следующим правилам:

- Если J=K=0, режим триггера не меняется.

- Когда J и K равны 1, происходит изменение состояния элемента на противоположное при поступлении каждого тактового импульса. В этом случае триггер функционирует идентично делителю частоты. Такой режим работы называют счётным, поскольку его использование позволяет осуществлять подсчёт определённых событий.

- При K = 1, J = 0 выходное значение принимает нулевое значение.

- Если K = 0, J = 1, тогда на выходе будет получена единица.

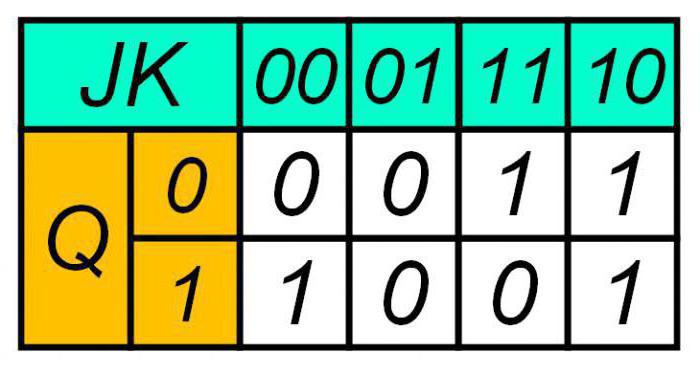

Алгоритм работы отображает таблица истинности JK-триггера, так как каждой входной комбинации значений соответствует строго определённая выходная.

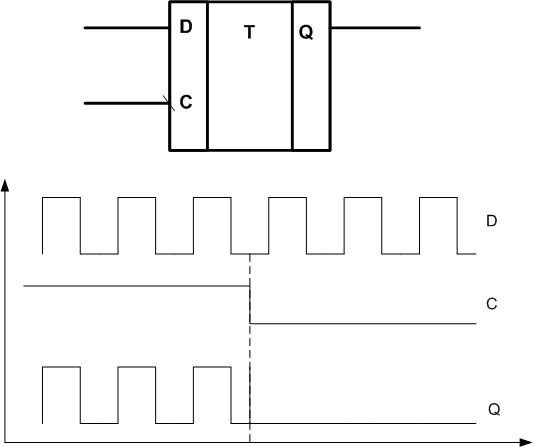

Разобраться в работе триггера помогает еще временная диаграмма, на которой графически отображаются сигнальные импульсы, присутствующие одновременно на входах и выходах устройства.

На приведённой диаграмме срабатывание происходит по фронту импульса C с задержкой. Момент, когда это происходит, зависит от конкретной схемы реализации.

Как реализованы функции JK-триггера

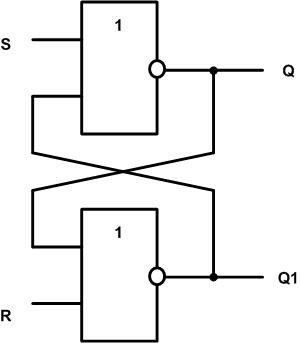

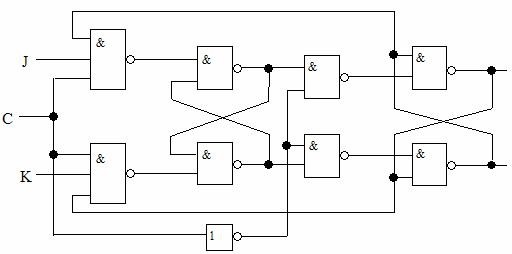

JK-тригер описание и схема которого были представлены выше, собран на основе четырех элементов И-НЕ. На вход каждого из них поступают двоичные значения, которые преобразуются по закону конъюнкции. Это электронное устройство имеет относительно несложную схему, работающую на основании простых логических операций. Использование входа C позволяет рассматривать ситуацию для значений, которые подаются на вход или получаются с выхода в последовательные моменты времени. Последние обозначаются латинской буквой «n». Таким образом, в момент t (n) на выходе будет значение Q(n), а в следующий — Q(n+1).

Далее рассмотрим принцип работы универсального JK-триггера для каждой из возможных ситуаций. Для удобства описания использования микросхем И-НЕ они будут пронумерованы. Микросхема слева вверху схемы обозначена D1. Та, что под ней — D2. Находящаяся справа вверху — D3, справа внизу — D4.

На J и K нулевые значения

В этом случае на первых двух микросхемах применение логического элемента И приведёт к получению нуля, но поскольку нужно брать дополнительное значение, будет образована единица на обеих микросхемах.

Так как выходное значение от Q и от отрицания Q будет подано на вход микросхем D3 и D4 (значение в момент времени n), то элемент И вместе с логической единицей просто передаст на выход это значение.

При этом необходимо учитывать, что значение отрицания Q будет подано на микросхему для формирования Q и наоборот. После этого на выходе микросхемы будет применено НЕ, которое сохранит прежнее значение. Таким образом, комбинация J = K = 0 приведёт к сохранению прежнего значения. Нужно помнить, что работа в соответствии с указанным алгоритмом возможна лишь в момент поступления отрицательного фронта сигнала на C. На протяжении остального времени ничего происходить не будет.

На J и K единичные значения

Если Q = 0, то отрицание Q будет равняться 1. Если на вход элемента D1 будет подано J = 1 и отрицание Q, тогда на выходе D1 сформируется ноль. С учетом того, что на входе D3 имеется логический 0, на выходе будет получена единица как результат функционирования элемента И-НЕ. Следовательно, в момент времени n + 1 сформируется инвертированное значение.

Для D2 и D4 значения находят аналогичным образом в соответствии с таблицей истинности JK-триггера.

J и K имеют противоположные значения

Если J = 1 и K = 0, то на вход D1 поступят сигналы J = 1 и отрицание Q. Результатом логического И станет отрицание Q. После инвертирования значение приобретает Q. На вход D3 поступят одновременно Q и отрицание Q. Поэтому результатом логического И всегда будет ноль. Этот результат не зависит от предыдущего значения отрицания Q.

В случае, когда J = 0, K = 1 аналогичным образом можно убедиться, что Q = 0.

Области применения триггера

JK-триггер можно рассматривать как ячейку памяти объёмом в 1 бит. Подача управляющих сигналов позволяет устанавливать значение памяти, равное 0 или 1, сохранять или инвертировать его, что наглядно демонстрирует таблица переходов.

На практике JK-устройства выпускают в виде микросхем, действующих в соответствии с таблицей истинности синхронного триггера. Обычно для того, чтобы запрограммировать определённый алгоритм сначала составляют логическую формулу преобразования двоичных сигналов. Затем реализовывают её в виде платы, включающей в себя установку триггеров.

Триггеры нашли широкое применение в таких компонентах вычислительных систем, как счетчики, регистры, процессоры и ОЗУ. Универсальность JK-триггеров позволяет использовать их в устройствах с разным уровнем сложности логики работы. Например, на основе JK-триггера можно собрать делитель частоты на 10. При поступлении на вход данного устройства импульсов частотой 10 кГц на выходе будут получены значения, равные 1 кГц. Подобные схемы получили название декадного делителя или декады.

Использование JK-устройств в составе цифровых счетчиков – это их основная область применения. Цифровые схемы в современной технике собираются на основе микросхем программируемой логики (FPGA) или заказных микросхем (ASIC).

Еще одна область применения JK-триггеров — устройства для обнаружения коротких импульсов. В данном случае импульс после поступления на вход С переходит в единичное состояние, которое затем обнаруживается последующей схемой, например, микропроцессором. Подобно схеме обнаружения КИ работает и схема ждущего мультивибратора.

При создании сложных логических схем нужны приборы разных видов. Поэтому выгоднее использовать универсальный тип устройства, которое может работать в различных режимах. Именно такими устройствами являются JK-триггеры.

Видео по теме

JK-триггер

–это триггер с двумя сигнальными и

одним синхронным входами.

Такие триггеры

часто называются универсальными, так

как на их основе можно получить RS- и

T-триггеры.

Название выводов

у таких триггеров пошло от английских

слов jerh -резкий толчок, kill — убить

Назначение-

JK-триггеров универсальное.

Выполняется

JK-триггер по двухступенчатой схеме с

использованием основного и вспомогательного

RS-триггера соединённых последовательно

и имеющих обратную связь..

JK-триггеры получили

следующее условное обозначение:

Рис. 0.26

Микросхемы

JK-триггеров имеют обозначение ТВ.

Например JK-триггер исполненный в

комплекте микросхем 555 серии имеет

обозначение — 555ТВ9.

Информационные

входы J и K аналогичны входам S и R

тактируемого RSC- триггера.

Принцип

действия JK-триггеров аналогичен RSC

триггеру, но JK-триггеры не имеют

запрещающей комбинации. Т.е. во время

действия тактового импульса сигнал

записывается в основной триггер, а в

момент окончания сигнал считывается

вспомогательным RS-триггером.

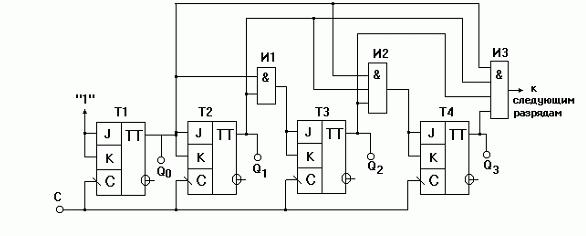

Схема JK-триггеров.

Рис.

Рис.

0.27

На схеме,

представленной выше, входы J, K являются

информационными входами. Они аналогичны

S и R входам тактируемого RSC-триггера (R

эквивалентен K входу, S — J входу).

Работу (изменение

состояний) JK — триггера при С=1 можно

представить в виде следующей таблицы.

-

Jn

Kn

Qn+1

0

0

Qn

1

0

1

0

1

0

1

1

При J=1, К=0 по срезу

тактового импульса триггер устанавливается

в единичное состояние, т.е. Q=1.

При J=0, К=1 —

переключается в нулевое состояние, т.е.

Q=0.

При J=0, К=0 — хранит

раннее записанную информацию.

В данном триггере

так же возможно осуществление счётного

режима. Сказанное происходит при J=К=1.

Триггер переключается каждым счетным

импульсом приходящим на вход С..

Рассмотрим работу

JK — триггера более подробно.

При J=K=0 на выходах

DD1 и DD2 устанавливаются 1, которые для

триггеров с инверсными входами являются

пассивными сигналами. Следовательно,

триггер Т1 и JK — триггер в целом своего

состояния не изменяет.

Чтобы на выходе

DD1 появился 0, необходимо чтобы J=1, C=1,

![]() =1.

=1.

Тогда триггер Т1 переходит в 1 состояние,

а по срезу тактового импульса и триггер

Т2 переходит в 1. Следовательно, Q2=1.

При К=1, С=1, Q=1 на

выходе DD2 появляется 0, переводящая

триггер Т1 в нулевое состояние, а по

срезу триггер Т2 в 0 и, следовательно, JK

— триггер в целом переходит в нулевое

состояние (Q=0,

![]() =1).

=1).

В отличие от RSC —

триггеров одновременное присутствие

единицы на сигнальных входах JK не

является запрещающей комбинацией. При

этом JK — триггер работает в счетном

режиме, т.е. переключается спадом каждого

тактирующего импульса.

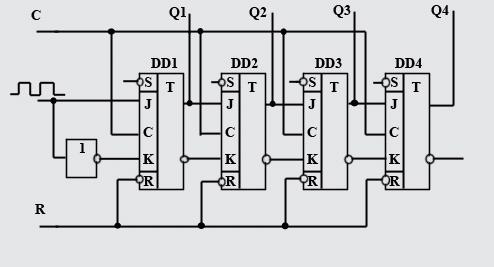

На базе JК — триггеров

можно построить любой из ранее

рассмотренных.

Т-триггер.

D-триггер.

Рис. 0.28

Синхронный

RS-триггер. Асинхронный Т-триггер.

Рис. 0.29

Заключение:

-

Интегральные

триггеры отличаются от триггеров на

дискретных элементах компактностью и

меньшим потреблнением энергии. Параметры

импульсов интегральных триггеров лучше

(tф

tс). -

Интегральные

триггеры используются в цифровой

технике как счетчики, делители частоты,

ячейки памяти и т.д. -

Основные типы

цифровых устройств, как то счётчики,

регистры, запоминающие устройства и

т.д. в основе своей структуры имеют

триггеры. -

Наиболее удобным

и универсальным в применении является

JK-триггер

Соседние файлы в папке Цифровые

- #

- #

- #

- #

Триггер — что это за устройство

Он представляет собой электронное устройство, способное на протяжении длительного времени сохранять одно из двух или нескольких состояний. Это происходит до тех пор, пока на него подаётся электропитание. Существует несколько типов триггеров, каждый из которых имеет свою сферу применения. Фактически они являются базовыми элементами. На их основе создаются различные цифровые электронные устройства.

Триггер способен на протяжении довольно длительного промежутка времени пребывать в одном устойчивом режиме из нескольких возможных, а затем под действием входных сигналов переходить из одного режима в другой. Состоит он из элементарных логических элементов, функционирующих по правилам математической логики. Это могут быть ИЛИ-НЕ и И-НЕ. Первые из них функционируют в одноединичном прямом коде, то есть, на выходе одного из элементов будет 1, а на выходах других — 0. Устройство с элементами второго вида работает в однонулевом инверсном коде: на выходе одного из них 0, а на выходах других — 1.

Триггер – элемент цифровой техники, бистабильное устройство, которое переключается в одно из состояний и может находиться в нем бесконечно долго даже при снятии внешних сигналов. Он строится из логических элементов первого уровня (И-НЕ, ИЛИ-НЕ и т.д.) и относится к логическим устройствам второго уровня.

На практике триггеры выпускаются в виде микросхем в отдельном корпусе или входят в качестве элементов в состав больших интегральных схем (БИС) или программируемых логических матриц (ПЛМ).

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

- асинхронные;

- синхронные (тактируемые).

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

- динамические;

- статические.

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

RS-триггер

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

- S — set (установка);

- R — reset (сброс).

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

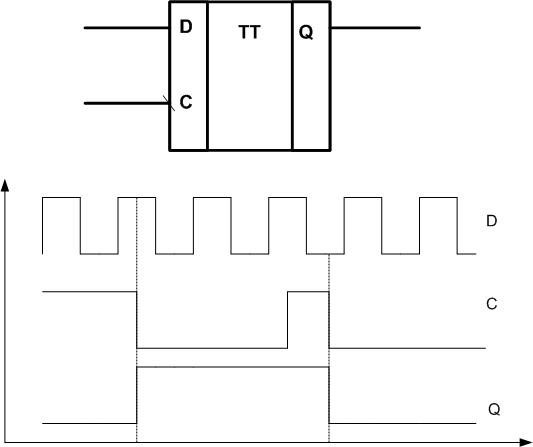

D-триггер («прозрачный триггер», «защелка», latch) относится к категории синхронных устройств, тактируемых по входу С. Также имеется вход для данных D (Data). По функциональным возможностям устройство относится к триггерам с приёмом информации по одному входу.

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

Прозрачность D-триггера не всегда является полезным свойством. Чтобы её избежать, применяются двойные элементы (flip-flop, «хлопающий» триггер), они обозначаются литерами TT. Первым триггером служит обычная защёлка, пропускающая входной сигнал на выход. Второй триггер служит элементом памяти. Тактируются оба устройства одним стробом.

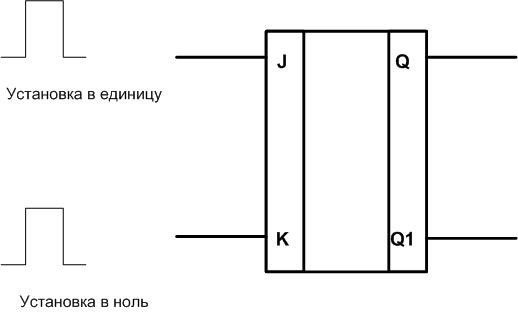

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

Универсальный триггер

JK-триггер

JK-триггером называют автомат Мура с двумя устойчивыми состояниями и двумя входами J и K, который при условии J * K = 1 осуществляет инверсию предыдущего состояния (т.е. при J*K=1, Q(t+1) = Q(t)), а в остальных случаях функционируют в соответствии с таблицей истинности RS триггера, при этом вход J эквивалентен входу S, а вход K — входу R. Этот триггер уже не имеет запрещенной комбинации входных сигналов и его таблица истинности, то есть зависимость Q(t+1) = f[J, K, Q(t)] имеет вид:

Таблица истинности JK-триггера:

По этой таблице можно построить диаграмму Вейча для Q(t+1), которую можно использовать для минимизации, и матрицу переходов:

Матрица переходов JK-триггера:

| J | K | Q(t) | Q(t+1) |

| b1 | |||

| b2 | |||

| b3 | |||

| b4 |

| ____ | _ | |||

| Q(t+1) = J* | Q(t) | v | K | *Q(t) |

В интегральной схемотехнике применяются только тактируемые (синхронные) JK триггера, которые при C=0 сохраняют свое состояние, а при C=1 работают как асинхронные JK триггера.

Триггер JK относится к разряду универсальных триггеров, поскольку на его основе путем несложной внешней коммутации можно построить RS-, D— и T— триггера. RS-триггер получается из триггера JK простым наложением ограничения на комбинацию входных сигналов J=K=1, так как эта комбинация является запрещенной для RS триггера.

Счетный триггер на основе JK триггера получается путем объединения входов J и K.

Триггер задержки (D-триггер) строится путем подключения к входу K инвертора, на который подается тот же сигнал, что и на вход J. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Структурная схема конечного автомата

В структурной теории автомат представляют в виде композиции двух частей: запоминающей части, состоящей из элементов памяти, и комбинационной части, состоящей из логических элементов:

Комбинационная схема строится на логических элементах, образующих функционально полную систему, а память – на элементарных автоматах, обладающих полной системой переходов и выходов.

Каждое состояние абстрактного автомата ai, где i={0, n}, кодируется в структурных автоматах набором состояний элементов памяти Qi, r={1,R}. Поскольку в качестве элементов памяти используются обычные триггера, то каждое состояние можно закодировать двоичным числом ai = Q1a1Q2a2… Qrar. Здесь аi={0, 1}, a Q – состояние автомата . Отсюда:

Общее число необходимых элементов памяти можно определить из следующего неравенства . Здесь (n+1) – число состояний. Логарифмируя неравенство получим . Здесь ]C [ — означает, что необходимо взять ближайшее целое число, большее или равное C.

В отличии от абстрактного автомата, имеющего один входной и один выходной каналы, на которые поступают сигналы во входном X={x1,x2,…,xm} и выходном Y={y1,y2,…,yk} алфавитах, структурный автомат имеет L входных и Nвыходных каналов. Каждый входной xj и выходной yj сигналы абстрактного автомата могут быть закодированы двоичным набором состояний входных и выходных каналов структурного автомата.

| xi = o1a1 o2a2… oLaL |

| yg = Z1a1Z2a2… ZNaN |

Здесь ofи Zh– состояния входных и выходных каналов соответственно.

Очевидно число каналов L и N можно определить по формулам ; , аналогичным формуле для определения R.

Изменение состояния элементов памяти происходит под действием сигналов U=(U1,U2,…,Ur), поступающих на их входы. Эти сигналы формируются комбинационной схемой II и называются сигналами возбуждения элементарных автоматов. На вход комбинационной схемы II, кроме входного сигнала xj, по цепи обратной связи поступают сигналы Q=(Q1, Q2, …, QR), называемые функцией обратной связи от памяти автомата к комбинационной схеме. Комбинационная схема I служит для формирования выходного сигнала yg, причем в случае автомата Мили на вход этой схемы поступает входной сигнал xj, а в случае автомата Мура – сигнал xj не поступает, так как yg не зависит от xj.

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С – тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер “сбросится” в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод – это корпус, а 14 вывод – это напряжение питания +5V. На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или “корпус”.

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто “висит” в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Возможности

Также важным отличием данных моделей является то, что в них устранена неопределенность, которая может возникнуть в случае, если входные сигналы будут поданы в определённой комбинации. Также существенным преимуществом является тот факт, что они могут выполнять функционал T-, D- и RS-триггеров. Комбинированный тип имеет дополнительные асинхронные входы, которые используются для предварительной установки приборов в определённое состояние. Примитивный JK можно получить из RS, у которого есть динамическое управление. Для этого необходимо его дополнить обратными связями с выходов на входы. Для получения Т-триггера необходимо на входы подать уровень напряжения, который установит логическую единицу.

В каких состояниях может быть главный герой статьи? Существует два принципа действий: асинхронный и синхронный. Во время первого происходит обмен данных независимо от входов. Синхронный JK-триггер действует одновременно, и из-за требований он является основным используемым элементом.

Чтобы своими глазами увидеть, что и как работает, необходимо JK-триггер включить на макетной плате и собственноручно подавать различные входные сигналы. Это сродни обучению на гитаре – можно изучить десятки самоучителей, но пока не возьмете в руки гитару, вы никогда не научитесь. Так же и со схемами: без опыта разобраться во всём сложно. Для наблюдения можно подсоединить светодиодные индикаторы к инверсному и прямому выходу. При желании положение дел можно наблюдать и благодаря обычному вольтметру, но в связи с размерами данный вариант не очень удобный, если говорить о такой вещи, как JK-триггер.

Таблица истинности

Что такое таблица истинности? Это специальный набор данных, который описывает логическую функцию. Что под ней понимают? В данном случае имеют в виду функцию, в которой значения параметров и её самой выражают логическую истинность. В качестве примера очень к месту будет вспомнить двузначную логику, где можно дать только два определения: ложь или истина. В качестве заменителей, когда говорят о компьютерных технологиях, часто вводят понятие 0 или 1. Причем использование данного инструментария оказалось удобным не только с позиции логики, но и при изображении в табличном варианте. Особенно часто их можно встретить в булевой алгебре или аналогичных системах логики. Но хватит информации, давайте посмотрим, как выглядит таблица JK-триггера.

| J | K | C | Q(t) | Q(t+1) | Пояснения |

| ноль | х | ноль | ноль | ноль | Хранится информация |

| ноль | х | ноль | единица | единица | |

| ноль | ноль | единица | ноль | ноль | Хранится информация |

| ноль | ноль | единица | единица | единица | |

| единица | ноль | единица | ноль | единица | Установлена логическая единица, вход J равен единице |

| единица | ноль | единица | единица | единица | |

| ноль | единица | единица | ноль | ноль | Устанавливается логический нуль, при этом K равно единице |

| ноль | единица | единица | единица | ноль | |

| единица | единица | единица | ноль | единица | счетный режим триггера K=J=1 |

Области применения триггера

JK-триггер можно рассматривать как ячейку памяти объёмом в 1 бит. Подача управляющих сигналов позволяет устанавливать значение памяти, равное 0 или 1, сохранять или инвертировать его, что наглядно демонстрирует таблица переходов.

На практике JK-устройства выпускают в виде микросхем, действующих в соответствии с таблицей истинности синхронного триггера. Обычно для того, чтобы запрограммировать определённый алгоритм сначала составляют логическую формулу преобразования двоичных сигналов. Затем реализовывают её в виде платы, включающей в себя установку триггеров.

Триггеры нашли широкое применение в таких компонентах вычислительных систем, как счетчики, регистры, процессоры и ОЗУ. Универсальность JK-триггеров позволяет использовать их в устройствах с разным уровнем сложности логики работы. Например, на основе JK-триггера можно собрать делитель частоты на 10. При поступлении на вход данного устройства импульсов частотой 10 кГц на выходе будут получены значения, равные 1 кГц. Подобные схемы получили название декадного делителя или декады.

Использование JK-устройств в составе цифровых счетчиков – это их основная область применения. Цифровые схемы в современной технике собираются на основе микросхем программируемой логики (FPGA) или заказных микросхем (ASIC).

Еще одна облать применения JK-триггеров — устройства для обнаружения коротких импульсов. В данном случае импульс после поступления на вход С переходит в единичное состояние, которое затем обнаруживается последующей схемой, например, микропроцессором. Подобно схеме обнаружения КИ работает и схема ждущего мультивибратора.

При создании сложных логических схем нужны приборы разных видов. Поэтому выгоднее использовать универсальный тип устройства, которое может работать в различных режимах. Именно такими устройствами являются JK-триггеры.

Предыдущая

РадиодеталиЧто такое SMD компоненты?

Следующая

РадиодеталиСистема уравнивания потенциалов

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

На рисунке видно, что JK-триггер имеет пять входов, в том числе прямой Q и инверсный выходы Q.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С — тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер «сбросится» в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод — это корпус, а 14 вывод — это напряжение питания +5V. На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или «корпус».

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто «висит» в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

-

Основы цифровой электроники.

В радиоэлектронике существует множество механизмов и деталей, которые с помощью простейших операций позволяют создавать сложные машины. Правда, для такой цели их нужно очень много. И одним из важнейших механизмов подобного предназначения являются JK-триггеры. Они позволяют обеспечить машинную логику для выполнения простейших логических операций. Как это осуществляется? Как необходимо подключать JK-триггер? Как выглядит таблица истинности? На эти и другие вопросы можно будет найти ответы в рамках статьи.

Что такое триггер?

Триггерами называют целый класс электронных устройств, которые имеют такое свойство, как длительное нахождение в одном из двух устойчивых состояний. Чередование осуществляется под воздействием внешних сигналов. Текущее состояние триггера с легкостью распознаётся благодаря наличию выходного напряжения. Отличительной способностью всего класса является свойство запоминать двоичную информацию. Тут возникает вопрос: есть ли у триггеров память? В обычном понимании нет. Но, тем не менее, они остаются в одном из 2 состояний, причем и после прекращения подачи сигнала. Благодаря этой особенности и считается, что они могут запоминать двоичную информацию.

При изготовлении триггеров на данный момент применяют полупроводниковые приборы (обычно полевые и биполярные транзисторы). Раньше использовали электронные лампы и электромагнитные реле. Своё применение триггеры нашли в интеграционных средах разработки, которые создаются для различных программируемых логических интегральных схем. Если говорить конкретнее, то их используют, чтобы организовать компоненты вычислительных систем: счетчики, регистры, процессоры и ОЗУ.

Триггеры

Триггеры и регистры являются простейшими представителями цифровых микросхем, имеющих внутреннюю память. Если выходные сигналы логических элементов и комбинационных микросхем однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Именно поэтому их применение позволяет строить гораздо более сложные и интеллектуальные цифровые устройства, чем в случае простейших микросхем без памяти. Микросхемы с внутренней памятью называются еще последовательными или последовательностными, в отличие от комбинационных микросхем.

Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания. Иначе говоря, их память относится к типу оперативной

(в отличие от

постоянной памяти

и

перепрограммируемой постоянной памяти

, которым отключение питания не мешает сохранять информацию). После выключения питания и его последующего включения триггеры и регистры переходят в случайное состояние, то есть их выходные сигналы могут устанавливаться как в уровень логической единицы, так и в уровень логического нуля. Это необходимо учитывать при проектировании схем.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Именно поэтому триггеры и регистры иногда называют также сверхоперативной памятью

. Однако недостаток триггеров и регистров в том, что объем их внутренней памяти очень мал, они могут хранить только отдельные сигналы, биты (триггеры) или отдельные коды, байты, слова (регистры).

Триггер можно рассматривать как одноразрядную, а регистр — как многоразрядную ячейку памяти, которая состоит из нескольких триггеров, соединенных параллельно (обычный, параллельный регистр) или последовательно (сдвиговый регистр или, что то же самое, регистр сдвига).

Триггеры

Принцип работы и разновидности триггеров

В основе любого триггера (англ. — «тrigger» или «flip-flop») лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

Рис. 7.1.

Схема триггерной ячейки

Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

Таблица 7.1. Таблица истинности триггерной ячейки

| Входы | Выходы | ||

| -R | -S | Q | -Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Без изменения | |

| 0 | 0 | Не определено |

В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

- RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый (а).

- JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко (б).

- D-триггер (обозначается ТМ) — наиболее распространенный тип триггера (в).

Примером RS-триггера является микросхема ТР2, в одном корпусе которой находятся четыре RS-триггера. Два триггера имеют по одному входу –R и –S, а два других триггера — по одному входу –R и по два входа –S1 и –S2, объединенных по функции И. Все триггеры имеют только по одному прямому выходу. RS-триггер практически ничем не отличается по своим функциям от триггерной ячейки, рассмотренной ранее (см. рис. 7.1). Отрицательный импульс на входе –R перебрасывает выход в нуль, а отрицательный импульс на входе –S (или на любом из входов –S1 и –S2) перебрасывает выход в единицу. Одновременные сигналы на входах –R и –S переводят выход в единицу, а после окончания импульсов триггер попадает случайным образом в одно из своих устойчивых состояний. Таблица истинности триггера ТР2 с двумя входами установки –S1 и –S2 представлена в табл. 7.2.

Рис. 7.2.

Триггеры трех основных типов

Таблица 7.2. Таблица истинности RS-триггера ТР2

| Входы | Выходы | ||

| -R | -S | Q | -Q |

| 1 | 1 | 1 | Без изменения |

| X | 0 | 1 | 1 |

| 0 | X | 1 | 1 |

| 1 | 1 | 0 | 0 |

| X | 0 | 0 | Не определен |

| 0 | X | 0 | Не определен |

JK-триггер значительно сложнее по своей структуре, чем RS-триггер. Он относится к так называемым тактируемым триггерам, то есть он срабатывает по фронту тактового сигнала. Примером может служить показанная на рис. 7.2 микросхема ТВ9, имеющая в одном корпусе два JK-триггера со входами сброса и установки -R и -S. Входы -R и -S работают точно так же, как и в RS-триггере, то есть отрицательный импульс на входе -R устанавливает прямой выход в нуль, а инверсный — в единицу, а отрицательный импульс на входе -S устанавливает прямой выход в единицу, а инверсный — в нуль.

Однако состояние триггера может быть изменено не только этими сигналами, но и сигналами на двух информационных входах J и K и синхросигналом С. Переключение триггера в этом случае происходит по отрицательному фронту сигнала С (по переходу из единицы в нуль) в зависимости от состояний сигналов J и K. При единице на входе J и нуле на входе К по фронту сигнала С прямой выход устанавливается в единицу (обратный — в нуль). При нуле на входе J и единице на входе К по фронту сигнала С прямой выход устанавливается в нуль (обратный — в единицу). При единичных уровнях на обоих входах J и K по фронту сигнала С триггер меняет состояние своих выходов на противоположные (это называется счетным режимом).

Таблица 7.3. Таблица истинности JK-триггера ТВ9

| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 0 | 1 | Х | Х | Х | 1 | 0 |

| 1 | 0 | Х | Х | Х | 0 | 1 |

| 0 | 0 | Х | Х | Х | Не определено | |

| 1 | 1 | 1 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 0 | 0 | 0 | Не изменяется | |

| 1 | 1 | 1 0 | 1 | 1 | Меняется на проти-воположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | 0 | Х | Х | Не изменяется | |

| 1 | 1 | 0 1 | Х | Х | Не изменяется |

Рис. 7.3.

Временная диаграмма работы JK-триггера ТВ9

Таблица истинности триггера ТВ9 представлена в табл. 7.3, а временная диаграмма работы — на рис. 7.3.

Это триггер, который в случае получения на свои оба входа логической единицы меняет состояние своего выхода на противоположное значение. Одно из отличий от других подобных приборов – отсутствие запрещенных состояний, которые могут быть на основных входах. Как выглядит JK-триггер? Схема изображения может быть представлена с разной детализацией, а также зависимо от дополнений, которые были добавлены человеком. Как видите, в статье присутствуют различные изображения устройства. Также, используя базу JK-триггера, можно создать D- или Т-модель. Как вы сможете убедиться, просмотрев таблицу истинности, данный механизм в инверсное состояние переходит всегда, когда на оба входа осуществляется подача логической единицы. Различают два вида JK-триггеров:

- Универсальные.

- Комбинированные.

Назначение, схема и принцип работы JK-триггер

Главная Избранные Случайная статья Познавательные Новые добавления Обратная связь FAQ

⇐ ПредыдущаяСтр 6 из 9Следующая ⇒

JK-триггер с дополнительными асинхронными инверсными входами S и R

JK-триггер[18][19] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump

— прыжок) аналогичен входу

S у RS-триггера. Вход K (от англ. Kill

— убить) аналогичен входу

R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и Kучитываются только в момент тактирования, например по положительному фронтуимпульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и Kлогической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[20].

Алгоритм функционирования JK-триггера можно представить формулой

Условное графическое обозначение JK-триггера со статическим входом С

Назначение, схема и принцип работы счетчиков импульсов.

Электронный счетчик импульсов предназначен для подсчета количества импульсов, поступающих с измерительных датчиков на счетные входы (или один счетный вход) счетчика импульсов и пересчета их в требуемые физические единицы измерения путем умножения на заданный множитель (например, в метры, литры, штуки, килограммы и т. д.); подсчета суммарной выработки за смену, сутки, неделю, месяц и т. д.; управления исполнительными механизмами одним или несколькими дискретными выходами (чаще всего, в счетчиках импульсов в качестве дискретного выхода используется реле или оптопара).

Как правило, в качестве датчика применяется механический прерыватель илииндуктивный датчик (бесконтактный датчик) или энкодер.

Электронные счетчики импульсов могут иметь высокую степень защиты IP (степень защиты оболочки) от пыли и воды (например, IP65).

Счетчик импульсов (некоторые модели) может иметь встроенную функцию тахометра илирасходомера.

Электронные счетчики импульсов сохраняют результат измерений при исчезновении напряжения питания в течение неограниченного периода времени в энергонезависимой памяти (EEPROM). После возврата напряжения питания счет импульсов продолжается, начиная с сохраненного значения; некоторые модели счетчиков импульсов индицируют факт пропадания напряжения питания во время работы.

Некоторые модели имеют интерфейс для подключения к сети или компьютеру (например, RS485, RS232, CAN), а также аналоговый выход ЦАП, который может быть использован как для передачи информации другим контрольно-измерительным приборам управления исполнительными механизмами (например, электроприводом).

Кроме того, счётчики импульсов классифицируют по направлению счета (режиму работы):

суммирующие счетчики импульсов;

вычитающие счетчики импульсов;

реверсивные счетчики импульсов.

Импульсы от энкодера с определением направления вращения

Реверсивные счетчики импульсов чаще всего используются при работе с 2-х канальнымиэнкодерами или с двумя индуктивными датчиками, при этом:

автоматически счетчиком импульсов определяется направление вращения энкодера;

происходит увеличение в 4 раза разрешающей способности энкодера, то есть 1 полный импульс c энкодера счетчик импульсов превращает в 4 инкремента (см. рис. поясняющий работу счетчика импульсов в реверсивном режиме).

⇐ Предыдущая6Следующая ⇒

Возможности

Также важным отличием данных моделей является то, что в них устранена неопределенность, которая может возникнуть в случае, если входные сигналы будут поданы в определённой комбинации. Также существенным преимуществом является тот факт, что они могут выполнять функционал T-, D- и RS-триггеров. Комбинированный тип имеет дополнительные асинхронные входы, которые используются для предварительной установки приборов в определённое состояние. Примитивный JK можно получить из RS, у которого есть динамическое управление. Для этого необходимо его дополнить обратными связями с выходов на входы. Для получения Т-триггера необходимо на входы подать уровень напряжения, который установит логическую единицу.

В каких состояниях может быть главный герой статьи? Существует два принципа действий: асинхронный и синхронный. Во время первого происходит обмен данных независимо от входов. Синхронный JK-триггер действует одновременно, и из-за требований он является основным используемым элементом.

Таблица истинности

Что такое таблица истинности? Это специальный набор данных, который описывает логическую функцию. Что под ней понимают? В данном случае имеют в виду функцию, в которой значения параметров и её самой выражают логическую истинность. В качестве примера очень к месту будет вспомнить двузначную логику, где можно дать только два определения: ложь или истина. В качестве заменителей, когда говорят о компьютерных технологиях, часто вводят понятие 0 или 1. Причем использование данного инструментария оказалось удобным не только с позиции логики, но и при изображении в табличном варианте. Особенно часто их можно встретить в булевой алгебре или аналогичных системах логики. Но хватит информации, давайте посмотрим, как выглядит таблица JK-триггера.

| J | K | C | Q(t) | Q(t+1) | Пояснения |

| ноль | х | ноль | ноль | ноль | Хранится информация |

| ноль | х | ноль | единица | единица | |

| ноль | ноль | единица | ноль | ноль | Хранится информация |

| ноль | ноль | единица | единица | единица | |

| единица | ноль | единица | ноль | единица | Установлена логическая единица, вход J равен единице |

| единица | ноль | единица | единица | единица | |

| ноль | единица | единица | ноль | ноль | Устанавливается логический нуль, при этом K равно единице |

| ноль | единица | единица | единица | ноль | |

| единица | единица | единица | ноль | единица | счетный режим триггера K=J=1 |

Универсальный триггер

JK-триггер

JK-триггером называют автомат Мура с двумя устойчивыми состояниями и двумя входами J и K, который при условии J * K = 1 осуществляет инверсию предыдущего состояния (т.е. при J*K=1, Q(t+1) = Q(t)), а в остальных случаях функционируют в соответствии с таблицей истинности RS триггера, при этом вход J эквивалентен входу S, а вход K — входу R. Этот триггер уже не имеет запрещенной комбинации входных сигналов и его таблица истинности, то есть зависимость Q(t+1) = f[J, K, Q(t)] имеет вид:

Таблица истинности JK-триггера:

По этой таблице можно построить диаграмму Вейча для Q(t+1), которую можно использовать для минимизации, и матрицу переходов:

Матрица переходов JK-триггера:

| J | K | Q(t) | Q(t+1) |

| b1 | |||

| b2 | |||

| b3 | |||

| b4 |

| ____ | _ | |||

| Q(t+1) = J* | Q(t) | v | K | *Q(t) |

В интегральной схемотехнике применяются только тактируемые (синхронные) JK триггера, которые при C=0 сохраняют свое состояние, а при C=1 работают как асинхронные JK триггера.

Триггер JK относится к разряду универсальных триггеров, поскольку на его основе путем несложной внешней коммутации можно построить RS-, D— и T— триггера. RS-триггер получается из триггера JK простым наложением ограничения на комбинацию входных сигналов J=K=1, так как эта комбинация является запрещенной для RS триггера.

Счетный триггер на основе JK триггера получается путем объединения входов J и K.

Триггер задержки (D-триггер) строится путем подключения к входу K инвертора, на который подается тот же сигнал, что и на вход J. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Лекция 6. Структурная схема конечного автомата

В структурной теории автомат представляют в виде композиции двух частей: запоминающей части, состоящей из элементов памяти, и комбинационной части, состоящей из логических элементов:

Комбинационная схема строится на логических элементах, образующих функционально полную систему, а память – на элементарных автоматах, обладающих полной системой переходов и выходов.

Каждое состояние абстрактного автомата ai, где i={0, n}, кодируется в структурных автоматах набором состояний элементов памяти Qi, r={1,R}. Поскольку в качестве элементов памяти используются обычные триггера, то каждое состояние можно закодировать двоичным числом ai = Q1a1Q2a2… Qrar. Здесь аi={0, 1}, a Q – состояние автомата . Отсюда:

Общее число необходимых элементов памяти можно определить из следующего неравенства . Здесь (n+1) – число состояний. Логарифмируя неравенство получим . Здесь ]C [ — означает, что необходимо взять ближайшее целое число, большее или равное C.

В отличии от абстрактного автомата, имеющего один входной и один выходной каналы, на которые поступают сигналы во входном X={x1,x2,…,xm} и выходном Y={y1,y2,…,yk} алфавитах, структурный автомат имеет L входных и Nвыходных каналов. Каждый входной xj и выходной yj сигналы абстрактного автомата могут быть закодированы двоичным набором состояний входных и выходных каналов структурного автомата.

| xi = o1a1 o2a2… oLaL |

| yg = Z1a1Z2a2… ZNaN |

Здесь ofи Zh– состояния входных и выходных каналов соответственно.

Очевидно число каналов L и N можно определить по формулам ; , аналогичным формуле для определения R.

Изменение состояния элементов памяти происходит под действием сигналов U=(U1,U2,…,Ur), поступающих на их входы. Эти сигналы формируются комбинационной схемой II и называются сигналами возбуждения элементарных автоматов. На вход комбинационной схемы II, кроме входного сигнала xj, по цепи обратной связи поступают сигналы Q=(Q1, Q2, …, QR), называемые функцией обратной связи от памяти автомата к комбинационной схеме. Комбинационная схема I служит для формирования выходного сигнала yg, причем в случае автомата Мили на вход этой схемы поступает входной сигнал xj, а в случае автомата Мура – сигнал xj не поступает, так как yg не зависит от xj.

Реализация счетного режима

Как же сделан счетный режим? Для достижения цели используется перекрестная обратная связь. Благодаря такому механизму никогда не может создаться запрещённая комбинация. При этом особенность, что она перекрестная, вводит дополнительный режим работы – счетный. Так, когда на входы k и j подаются логические единицы одновременно, то JK-триггер переключается в счетный режим, подобно как и Т-модель.

Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными.

Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени.

Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q’ — логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q’ равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля.

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.

Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И.

Также такие триггеры нашли применение при конструировании сдвигающих регистров.

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.

Автоматические устройства такого типа удобно использовать при конструировании счетчиков (узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов). Например, на фото показан счетчик на JK-триггерах. Структурная организация двоичных счетчиков с параллельным переносом значительно упрощается, если их строить на приборах типа JK со встроенными логическими элементами И.

Также такие триггеры нашли применение при конструировании сдвигающих регистров.

Регистры сдвига – это узлы, выполняющие смещение двоичной информации вправо и влево по регистру в зависимости от управляющих сигналов.

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

На рисунке видно, что JK-триггер имеет пять входов, в том числе прямой Q и инверсный выходы Q.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С — тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер «сбросится» в нулевое состояние. Когда

J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод — это корпус, а 14 вывод — это напряжение питания +5V. На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или «корпус».

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто «висит» в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно

ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

go-radio.ru

JK-триггер. Принцип работы, фунцкциональные схемы, таблицы истинности

Триггер представляет собой элементарный цифровой автомат. Он имеет два состояния устойчивости. Одному из них присваивается значение «1», а другому — «0».

По способу реализации логических связей различают следующие виды упомянутых устройств: JK-триггер, RS-триггер, T-триггер, D-триггер и т. д.

Предметом нашего сегодняшнего разговора являются автоматы типа JK. Они отличаются от RS-приборов тем, что при подаче на вход информации, запрещенной для RS-триггеров, инвертируют хранимые в них сведения.

Представляем вашему вниманию таблицу переходов, которая описывает работу JK-триггера. При минимизации каты Карно выводится характеристическое уравнение для рассматриваемого устройства: Q(t+1)=K’t Qt V Jt Q’t.

Из таблицы видно, что состояние прибора определяется не только значениями информации на входах J и K, но и состоянием на выходе Qt, которое ранее определяло JK-триггер. Это позволяет строить функциональные схемы таких устройств на двухступенчатых автоматах типа RS. JK-приборы бывают синхронными и асинхронными.

Для проектирования JK-триггера из двухступенчатого устройства RS синхронного типа требуется соединить обратные связи выходов двухступенчатого автомата RS со входами логических элементов его первой ступени.

Принцип работы JK-триггера: если на информационных (J и K) входах устройства подан уровень нуля, то на выходе элементов И-НЕ (1 и 2) устанавливается уровень единицы, и JK-триггер сохранит свое состояние. Например, Q будет равен логическому нулю, Q’ — логической единице. В таком случае при подаче сигналов J и C, равных логической единице, на входе элемента И-НЕ1 устанавливается логический нуль и, соответственно, уровень логической единицы на входе первого T-триггера. При снятии синхронизирующего сигнала (С равен нулю) состояние упомянутого устройства Т-типа уровнем логического нуля с выхода И=НЕ3 передастся на вход второго T-триггера. В результате JK-триггер переключится в состояние логической единицы (в таком случае Q равен единице, а Q’ равен нулю). Теперь, если на входе триггера (К и С) подается сигнал, равный логической единице, то на выходе элемента И-НЕ2 логический нуль установит первый Т-триггер в состояние нуля. После снятия синхронизирующего сигнала с выхода элемента И-НЕ4 логический нуль передастся на вход второго автомата типа Т, и JK-триггер переключается в состояние логического нуля.

При проектировании сложных логических схем необходимы приборы разных типов. Поэтому выгоднее изготовить универсальный тип устройства, которое можно использовать в различных режимах работы и модификациях. В интегральной схемотехнике наибольшее распространение получили синхронные D- и JK-триггеры. В электронно-вычислительных машинах широко используют цифровые автоматы JK типа с групповыми J, K и дополнительными установочными R, S-входами. Каждая группа объединена конъюнкцией, что позволяет расширить логические возможности и JK-триггера.