Процессоры

Режимы процессора

- Подробности

- Родительская категория: Процессоры

- Категория: Принципиальное устройство процессора

Режимы процессора

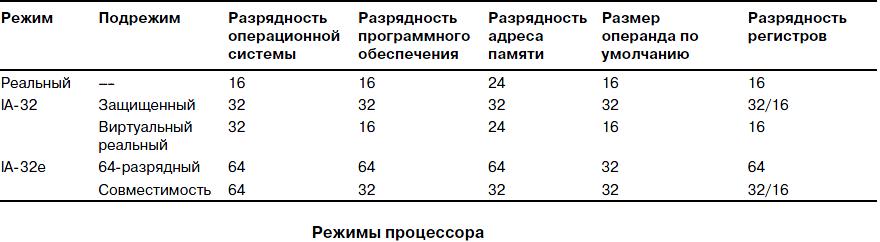

Все 32-разрядные и более поздние процессоры Intel, начиная с 386-го, а также совместимые с ними могут выполнять программы в нескольких режимах. Режимы процессора предназначены для выполнения программ в различных средах; в разных режимах возможности чипа неодинаковы, потому что команды выполняются по разному. В зависимости от режима процессора изменяется схема управления памятью системы и задачами. Процессоры могут работать в трех режимах.

- Реальный режим (16-разрядное программное обеспечение).

- Режим IA-32:

• защищенный режим (32-разрядное программное обеспечение);

• виртуальный реальный режим (16-разрядное программное обеспечение в 32-разрядной среде). - Расширенный 64-разрядный режим IA-32e (также называемый AMD64, x86-64 и EM64T):

• 64-разрядный режим (64-разрядное программное обеспечение);

• режим совместимости (32-разрядное программное обеспечение).

Реальный режим

Реальный режим иногда называют режимом 8086, поскольку он основан на инструкциях процессоров 8086 и 8088. В первом IBM PC использовался процессор 8088, который мог выполнять 16-разрядные команды, применяя 16-разрядные внутренние регистры, и адресовать только 1 Мбайт памяти, используя для адреса 20 разрядов. Все программное обеспечение PC первоначально было предназначено для этого процессора; оно было разработано на основе 16-разрядной системы команд и модели памяти объемом 1 Мбайт. Например, операционные системы DOS и Windows от 1.x до 3.x, а также все приложения для этих ОС написаны в расчете на 16-разрядные команды. Эти 16-разрядные операционные системы и приложения были разработаны для выполнения на первоначальном процессоре 8088.

Более поздние процессоры, например 286, также могли выполнять те же самые 16-разрядные команды, что и первоначальный 8088, но намного быстрее. Другими словами, процессор 286 был полностью совместим с первоначальным 8088 и мог выполнять все 16-разрядные программы точно так же, как 8088, только значительно быстрее. 16-разрядный режим, в котором выполнялись команды процессоров 8088 и 286, был назван реальным режимом. Все программы, выполняемые в реальном режиме, должны использовать только 16-разрядные команды, 20-разрядные адреса и поддерживаться архитектурой памяти, рассчитанной на емкость до 1 Мбайт. Для программного обеспечения этого типа обычно используется однозадачный режим, т.е. одновременно может выполняться только одна программа. Нет никакой встроенной защиты для предотвращения перезаписи ячеек памяти одной программы или даже операционной системы другой программой; это означает, что при выполнении нескольких программ вполне могут быть испорчены данные или код одной из них, что может привести всю систему к краху (или останову).

Режим IA»32 (32″разрядный)

Первым 32-разрядным процессором, предназначенным для PC, был 386-й. Этот чип мог выполнять абсолютно новую 32-разрядную систему команд. Чтобы полностью использовать преимущество 32-разрядной системы команд, были необходимы 32-разрядная операционная система и 32-разрядные приложения. Этот новый режим назывался защищенным, так как выполняемые в нем программы защищены от перезаписи своих областей памяти другими программами. Такая защита делает систему более надежной, поскольку ни одна программа с ошибками уже не сможет так легко повредить другие программы или операционную систему. Кроме того, программу, “потерпевшую крах”, можно довольно просто завершить без ущерба для всей системы.

Зная, что для разработки новых операционных систем и приложений, использующих преимущества 32-разрядного защищенного режима, потребуется некоторое время, Intel предусмотрела в процессоре 386 обратно совместимый реальный режим. Благодаря этому процессор 386 мог выполнять немодифицированные 16-разрядные приложения, причем намного быстрее, чем на любом процессоре предыдущего поколения. Для большинства пользователей этого было достаточно; им не требовалось все 32-разрядное программное обеспечение — достаточно было того, что имевшиеся у них 16-разрядные программы работали быстрее. К сожалению, из-за этого процессор никогда не работал в 32-разрядном защищенном режиме и все возможности защищенного режима не использовались.

Когда высокопроизводительный процессор, подобный Pentium 4, работает в DOS (т.е. в реальном режиме), он напоминает “Turbo 8088”. Слово “Turbo” означает, что процессор имеет преимущество в быстродействии при выполнении 16-разрядных программ, хотя он может выполнять только 16-разрядные команды и обращаться к памяти в пределах все того же 1 Мбайт, предусмотренного картой памяти процессора 8088. Поэтому, даже если у вас система с Pentium 4 или Athlon XP и оперативной памятью емкостью 256 Мбайт, при работе в Windows 3.x или DOS в действительности используется только первый мегабайт памяти. В связи с этим потребовались новые операционные системы и приложения, которые могли бы использовать все преимущества современных процессоров в 32-разрядном защищенном режиме. Однако некоторые пользователи поначалу сопротивлялись переходу к 32-разрядной среде. Сообщество пользователей оказалось весьма устойчивым в своих привязанностях и не желало изменять привычек. Признаюсь честно: я был одним из них.

Из-за сопротивления пользователей 32-разрядные операционные системы, такие как Unix и ее разновидности (например, Linux), OS/2 и даже Windows NT/2000/XP, распространялись на рынке ПК довольно вяло. Из перечисленных систем Windows XP стала по настоящему широко распространенным программным продуктом во многом благодаря огромной популярности Windows 95/98/Me (смешанные 16/32-разрядные системы). Последней полностью 16-разрядной операционной системой была Windows серии 3.x, так как на самом деле она работала в качестве надстройки DOS.

Такие 64-разрядные процессоры, как Itanium, AMD Opteron и EM64T-совместимый процессор Xeon, привнесли возможность работы 64-разрядных программ в серверных системах, в то время как процессоры Athlon 64, EM64T-совместимый Pentium 4, а также Pentium D и Core 2 создавались непосредственно для настольных систем. Оба процессора совместимы со всем существующим 32-разрядным программным обеспечением. Но для того, чтобы воспользоваться возможностями процессора в полном объеме, потребуются полноценные 64-разрядные операционные системы и приложения. Microsoft уже выпустила 64-разрядные версии Windows XP и Vista, в то время как различными компаниями создаются 64-разрядные приложения для серверов и рабочих станций.

Примечание

В процессорах Itanium и AMD Athlon 64 реализованы различные 64-разрядные архитектуры. Таким образом, 64-разрядное программное обеспечение, созданное для одной платформы, будет несовместимо с другой и потребует отдельной перекомпиляции со стороны поставщика продукта. Одним словом, специально созданные программы для 64-разрядных процессоров Intel нельзя будет запустить на компьютере с 64-разрядным процессором Athlon и наоборот.Виртуальный реальный режим IA-32

Для обратной совместимости 32-разрядная система Windows использует третий режим в процессоре — виртуальный реальный режим. По существу, это режим выполнения 16-разрядной среды (реальный режим), реализованный внутри 32-разрядного защищенного режима (т.е. виртуально, а не реально). Выполняя команды в окне командной строки DOS системы Windows, вы создаете виртуальный сеанс реального режима. Поскольку защищенный режим является подлинно многозадачным, фактически можно выполнять несколько сеансов реального режима, причем в каждом сеансе собственное программное обеспечение работает на виртуальном компьютере. И все эти приложения могут выполняться одновременно, даже во время работы других 32-разрядных программ.

Учтите, что любая программа, выполняемая в виртуальном окне реального режима, может обращаться только к памяти объемом до 1 Мбайт, причем для каждой такой программы это будет первый и единственный мегабайт памяти в системе. Другими словами, если вы выполняете приложение DOS в виртуальном реальном окне, ему будет доступна память только объемом до 640 Кбайт. Так происходит потому, что в 16-разрядной среде имеется только 1 Мбайт общей оперативной памяти, при этом верхние 384 Кбайт зарезервированы для системы. Виртуальное реальное окно полностью имитирует среду процессора 8088, и, если не учитывать быстродействие, программное обеспечение будет выполняться точно так, как оно выполнялось первым PC в реальном режиме. Каждая виртуальная машина получает собственный 1 Мбайт адресного пространства и собственный экземпляр реальных аппаратных подпрограмм управления аппаратурой (базовую систему ввода-вывода), причем при этом эмулируются все регистры и возможности реального режима.

Виртуальный реальный режим используется при выполнении 16-разрядных программ в окне DOS. При запуске приложения DOS операционная система Windows создает виртуальную машину DOS, на которой это приложение может выполняться.

Важно отметить, что все Intel-совместимые процессоры (в частности, AMD и Cyrix) при включении питания начинают работать в реальном режиме. При загрузке 32-разрядная операционная система автоматически переключает процессор в 32-разрядный режим и управляет им в этом режиме.

Также важно заметить, что некоторые приложения DOS и Windows 3.x в 32-разрядной среде ведут себя неадекватно, т.е. делают то, что не поддерживается даже в виртуальном реальном режиме.

Диагностическое программное обеспечение — прекрасный тому пример: оно не будет корректно работать в окне реального режима (виртуального реального) под управлением Windows. Чтобы на Pentium 4 запустить такое программное обеспечение в первоначальном упрощенном режиме, необходимо прервать процесс начальной загрузки системы и просто загрузить DOS. Это можно выполнить в Windows 9x (исключая Windows Me), нажимая клавишу <F8>, когда на экране появляется подсказка Starting Windows. Затем, когда появится загрузочное меню, в нем нужно выбрать команду загрузки простой 16-разрядной операционной системы реального режима DOS. Для запуска программ диагностики, которые невозможно запустить обычным образом в защищенном режиме, рекомендуется выбирать режим с поддержкой командной строки. Учитывая, что промежуток времени, в который Windows ожидает нажатия <F8>, очень короткий (порядка 2 с), лучше нажимать <F8> несколько раз подряд. Операционная система Windows Me создавалась, как вы знаете, на основе Windows 98. Пытаясь отучить пользователей от 16-разрядного режима работы, Microsoft удалила опцию загрузочного меню (Startup). Операционные системы Windows NT/2000/XP также лишены возможности прервать загрузку подобным образом. Для запуска компьютера в режиме DOS придется создать загрузочный диск, который и будет затем использоваться для загрузки системы в реальном режиме. Как правило, этот режим требуется для некоторых процедур технического обслуживания, в частности для выполнения аппаратной диагностики и непосредственного редактирования секторов диска.

Хотя реальный режим используется DOS и “стандартными” приложениями DOS, есть специальные программы, которые “расширяют” DOS и открывают доступ к дополнительной памяти XMS (сверх 1 Мбайт). Они иногда называются расширителями DOS и обычно включаются как часть программного обеспечения DOS или Windows 3.x, в котором используются. Протокол, описывающий, как выполнять DOS в защищенном режиме, называется DPMI (DOS Protected Mode Interface — интерфейс защищенного режима DOS).

Этот протокол использовался в Windows 3.x для обращения к дополнительной памяти XMS при работе приложений для Windows 3.x. Он позволял 16-разрядным приложениям использовать память, превышающую 1 Мбайт. Расширители DOS особенно часто применяются в играх DOS; именно благодаря им игровая программа может использовать объем памяти, намного превышающий стандартный (1 Мбайт), который могут адресовать большинство программ, работающих в реальном режиме. Эти расширители DOS переключают процессор в реальный режим и обратно, а в случае запуска под управлением Windows применяют интерфейс DPMI, встроенный в Windows, и тем самым позволяют другим программам совместно использовать часть дополнительной памяти XMS системы.

Есть еще одно исключение: первые 64 Кбайт дополнительной памяти в реальном режиме доступны программам. Это результат ошибки в первом компьютере IBM AT, связанной с 21-й линией адреса памяти (A20, поскольку A0 — первая строка адреса). Управляя сигналом на линии A20, программное обеспечение реального режима может получать доступ к первым 64 Кбайт дополнительной памяти — это первые 64 Кбайт памяти, следующие за первым мегабайтом. Эта область памяти называется областью верхних адресов памяти (high memory area — HMA).

64″разрядный расширенный режим IA»32e (AMD64, x86″64, EM64T)

Этот режим процессора является расширением архитектуры IA-32, разработанным компанией AMD и в дальнейшем поддержанным Intel. Процессоры, поддерживающие 64-разрядные расширения, могут работать в реальном режиме (8086), режиме IA-32 или IA-32e. При использовании режима IA-32 процессор может работать в защищенном или виртуальном реальном режиме. Режим IA-32e позволяет работать в 64-разрядном режиме или в режиме совместимости, что подразумевает возможность одновременного выполнения 64- и 32-разрядных приложений. Режим IA-32e включает в себя два подрежима.

- 64-разрядный режим. Позволяет 64-разрядной операционной системе выполнять 64-разрядные приложения.

- Режим совместимости. Позволяет 64-разрядной операционной системе выполнять 32-разрядные приложения.

Первый подрежим активизируется после загрузки 64-разрядной операционной системы и используется 64-разрядными приложениями. В 64-разрядном подрежиме доступно несколько новых функций:

- 64-разрядная линейная адресация памяти;

- Поддержка физической памяти объемом более 4 Гбайт (определенные ограничения накладываются процессором);

- 8 новых регистров общего назначения GPR (General-Purpose Register);

- 8 новых регистров для поточных расширений SIMD (MMX, SSE, SSE2 и SSE3);

- 64-разрядные регистры GPR и указатели инструкций.

Режим совместимости IE-32e позволяет запускать 32- и 16-разрядные приложения под управлением 64-разрядной операционной системы. К сожалению, старые 16-разрядные программы, работающие в виртуальном реальном режиме (например, приложения DOS), не поддерживаются, а значит, их выполнение невозможно. Данное ограничение наверняка будет представлять наибольшую проблему для пользователей. Подобно 64-разрядному режиму, режим совместимости активизируется операционной системой для отдельных приложений, благодаря чему становится возможным одновременное выполнение 64- и 32-разрядных приложений.

Для того чтобы все эти приложения работали, необходима 64-разрядная операционная система и, что гораздо важнее, 64-разрядные драйверы для всех устройств, предназначенные именно для этой операционной системы. В настоящее время существуют три 64-разрядные версии Windows:

- Windows XP 64-bit Edition for Itanium;

- Windows XP Professional x64 Edition;

- Windows Vista 64-bit (несколько вариантов).

Первая из них, предназначенная для процессоров с архитектурой IA-64, таких как Itanium и Itanium 2, была представлена еще в 2001 году. Последние две предназначены для процессоров архитектуры IA-32e, поддерживающих 64-разрядные расширения, в частности Athlon 64, Opteron, некоторые модели Sempron, Core 2, Pentium D, Pentium Extreme Edition, а также некоторые модели Xeon и Pentium 4. Обратите внимание, что Microsoft использует термин x64применительно к процессорам, поддерживающим расширения AMD64 или EM64T, так как расширения стандартной архитектуры IA-32, разработанные AMD и Intel, практически идентичны и поддерживаются одной версией Windows.

Примечание

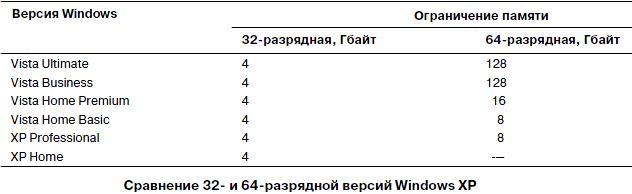

В первых версиях процессоров с технологией EM64T от компании Intel отсутствовала поддержка инструкций IAHF и SAHF набора команд AMD64. В то же время процессоры Pentium 4 и Xeon полностью поддерживают эти инструкции, однако требуется обновление BIOS. Новые многоядерные процессоры также поддерживают эти инструкции.Ограничения физической памяти для 32- и 64-разрядной версии редакций систем Windows XP и Vista представлены в таблице ниже .

Основное различие между 32- и 64-разрядной версиями Windows — поддерживаемый объем памяти, поскольку 32-разрядные версии не поддерживают более 4 Гбайт физической памяти, а также больше 2 Гбайт выделенной памяти на процесс. В то же время 64-разрядные версии Windows поддерживают до 128 Гбайт физической памяти (при выделении до 4 Гбайт на каждый 32-разрядный процесс, или до 8 Гбайт на каждый 64-разрядный процесс). Поддержка больших объемов памяти означает, что приложения могут загружать больше информации в память, а значит, процессор может быстрее обращаться к данным.

Следует отметить, что 64-разрядные версии Windows позволяют запустить без каких либо проблем 32-разрядные Windows-приложения, но не поддерживают приложения DOS и другие программы, работающие в виртуальном реальном режиме. Достаточно серьезная проблема связана и с драйверами: 32-разрядные процессы не могут загружать 64-разрядные динамически подключаемые библиотеки DLL, а 64-разрядные процессы, в свою очередь, не могут загружать 32-разрядные библиотеки DLL. Следовательно, для всех устройств, подключенных к системе, необходимы как 32-, так и 64-разрядные драйверы. Поиск 64-разрядных драйверов для старых устройств крайне сложен. Найти драйверы для устройств, выпуск которых давно прекращен, чаще всего просто невозможно. Даже для новых устройств может пройти пару лет, прежде чем их производители начнут поставлять 64-разрядные версии драйверов. Хочется верить, что в обозримом будущем все производители оборудования начнут выпускать драйверы для 64-разрядных систем. Прежде чем устанавливать 64-разрядную версию Windows, убедитесь в наличии 64-разрядных версий драйверов для всех имеющихся в компьютерной системе внутренних и внешних устройств. Не забывайте, что драйверы для Itanium-совместимых версий операционных систем не подходят для операционных систем с x64-совместимыми процессорами.

Рассматривая возможность перехода от 32- к 64-разрядной технологии, следует принимать во внимание поддерживаемый объем памяти, доступность драйверов и совместимость программного обеспечения. Как уже отмечалось, переход от 16-разрядных вычислений к 32-разрядным продолжался 16 лет. Конечно, переход от 32-разрядных вычислений к 64-разрядным не будет столько длиться, но 2–3 года на это все же уйдет.

4.1 Обзор режимов работы

Под

IA-32

подразумевается семейство процессоров

фирмы Intel,

родоначальником которого является

процессор Intel386.

В это семейство входит и процессор

Pentium 4.

Несмотря на то, что с момента выпуска

процессора Intel386

быстродействие процессоров и их

внутренняя структура существенно

изменились, для программиста эти отличия

не имеют особого значения, поскольку

все они скрыты «за ширмой» стандарта

IA-32.

Таким образом, с точки зрения программиста,

архитектура процессоров IA-32

по существу не изменилась с момента

выпуска процессора Intel386,

если не считать введения набора

высокопроизводительных команд для

поддержки мультимедийных приложений.

Процессоры

семейства IA-32

могут работать в одном из трех основных

режимов:

-

реальной

адресации

(Real-address mode); -

защищенном

(Protected mode); -

управления

системой

(System Management mode).

Кроме

того, существует еще один виртуальный

режим работы (Virtual-8086

mode),

или режим эмуляции процессора 8086, который

является разновидностью защищенного

режима.

В

семействе процессоров IA-32

выбор метода обращения к памяти

определяется режимом работы процессора.

Реальный

режим адресации.

В этом режиме полностью повторяется

работа процессора Intel

8086 и добавляется несколько новых

возможностей, например команды перехода

в другие режимы работы. Реальный режим

адресации использовался в операционных

системах Windows 95/98

в случае, когда приложению MS DOS

нужно было предоставить полный контроль

над аппаратным обеспечением компьютера.

Им часто пользовались при запуске старых

компьютерных игр в системах Windows

95/98. При выполнении начальной загрузки

по сигналу сброса (Reset)

все процессоры фирмы Intel

семейства IA-32

автоматически переходят в реальный

режим адресации. После этого операционная

система компьютера может переключить

процессор в требуемый режим работы.

В

реальном режиме

процессор

может обращаться только к первому

мегабайту памяти, адреса которого

находятся в диапазоне от 00000 до FFFFF

в шестнадцатеричном выражении. При этом

процессор работает в однозадачном

режиме (т.е. в заданный момент времени

он может выполнять только одну программу).

Однако при этом он может в любой момент

прервать ее выполнение и переключиться

на процедуру обработки запроса (его

называют прерыванием),

поступившего

от одного из периферийных устройств.

Любой программе, которую выполняет в

этот момент процессор, разрешен доступ

без ограничения к любым областям памяти,

находящимся в пределах первого мегабайта:

к ОЗУ – по чтению и записи, а к ПЗУ,

понятно, только по чтению. Реальный

режим работы процессора используется

в операционной системе MS

DOS,

а также в системах Windows 95

и 98 при загрузке в режиме эмуляции MS

DOS.

Защищенный

режим. Это

основной режим работы процессоров

IA-32, в котором для программиста доступны

все команды, режимы адресации и возможности

процессора. При этом каждой программе

выделяется изолированная область

памяти, состоящая из одного или нескольких

сегментов. В процессе работы процессор

отслеживает все обращения программы к

памяти и пресекает все попытки обращения

за пределы выделенных программе

сегментов, либо нарушение прав доступа

к сегменту, примером чего является

попытка записи данных в сегмент кода,

право доступа к которому определено

как readonly.

Именно это и определяет защищённость

программ как друг от друга, так и

защищённость данных и кода от самой

программы (неправильных её действий).

В

защищенном режиме процессор может

одновременно выполнять несколько

программ. При этом каждому процессу

(т.е. выполняющейся программе) может

быть назначено до 232 = 4 Гбайт

оперативной памяти. Чтобы предотвратить

взаимное влияние выполняющихся программ

друг на друга им выделяются изолированные

участки памяти (т.е. код и данные программ

находятся во взаимно несмежных сегментах).

В защищенном режиме работают такие

операционные системы, как MS Windows и

Linux.

Защищённый

режим основывается на дескрипторной

модели доступа к памяти. Кроме этого

современные операционные системы,

работающие в защищённом режиме, используют

страничную организацию памяти, которая

позволяет увеличивать размер линейного

адресного пространства, отводимого под

все запущенные приложения.

Виртуальный

режим. При

работе ЦПУ в защищенном режиме он может

непосредственно выполнять программы,

написанные для реального режима адресации

процессора i8086. Таким образом, становится

возможным запуск программ, написанных

для системы MS DOS в безопасном многозадачном

окружении. Другими словами, даже если

программа в процессе выполнения в

результате ошибки или сбоя «зависнет»,

это никак не повлияет на другие

выполняющиеся в данный момент программы.

Именно поэтому данный режим работы

часто называют режимом эмуляции

виртуального процессора 8086, хотя на

самом деле этот режим относится к

защищенному режиму работы процессора.

В

виртуальном режиме адресации для каждой

задачи создается собственная виртуальная

машина, которой выделяется изолированная

область памяти размером 1 Мбайт, и

полностью эмулируется работа процессора

80×86 в реальном режиме адресации. Например,

в операционных системах Windows 2000 и ХР

виртуальная машина процессора 8086

создается каждый раз при запуске

пользователем окна командного

интерпретатора (сеанса MS DOS). При этом

одновременно можно запустить довольно

много таких окон, причем выполняющиеся

в них программы не будут влиять друг на

друга. Однако не стоит обольщаться,

часть программ, написанных для системы

MS DOS и реального режима адресации,

напрямую взаимодействуют с аппаратным

обеспечением компьютера. Поэтому они

не будут работать в среде ОС Windows 2000

и ХР.

Режим

управления системой. Данный

режим работы процессора часто обозначают

аббревиатурой SSM (System Management mode). Он

позволяет предоставить операционной

системе компьютера механизм для

выполнения таких функций, как перевод

компьютера в режим энергосбережения и

восстановления работоспособности

системы после сбоя. Эти функции обычно

используются производителями компьютера

и материнских плат для установки нужных

режимов работы их оборудования.

Наиболее

полная информация о режимах работы

процессора содержится в трехтомной

фирменной документации, озаглавленной

IA-32

Intel

Architecture

Software

Developer‘s

Manual.

Её

можно загрузить с Web-сервера

фирмы Intel

по адресу: http://developer.intel.com.

Соседние файлы в предмете [НЕСОРТИРОВАННОЕ]

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

общие принципы работы (x86 CPU FAQ 1.0)

Disclaimer

Наверное, наиболее точно причину появления данного материала можно сформулировать так: «даже не столько нужно, чтобы он был — сколько странно, что его до сих пор не было». И действительно: в комментариях к результатам тестов, мы постоянно оперируем такими понятиями как «ёмкость кэша», «скорость процессорной шины», «поддержка расширенных наборов инструкций», но единой статьи, в которой были бы собраны разъяснения всех этих терминов — на сайте нет. Такое упущение, разумеется, следовало устранить. Данная статья с подзаголовком «x86 CPU FAQ» и является попыткой сделать это. Разумеется, некоторые её разделы могут быть отнесены не только к процессорам архитектуры x86, и не только с десктопным (предназначенным для установки в ПК) их вариантам, однако вот уж на такой глобализм мы совершенно точно не замахиваемся. Поэтому просьба помнить, что в рамках данного материала, если в явной форме не указано иное, слово «процессор» обозначает «процессор архитектуры x86, предназначенный для установки в десктопы». Возможно, в процессе дальнейшего совершенствования и расширения, появятся в статье разделы, посвящённые серверным CPU или даже процессорам других архитектур, но это уже дело будущего… Оглавление

- Введение

- Код и данные: основной принцип работы процессора

- Общие принципы взаимодействия процессора и ОЗУ

- Контроллер памяти

- Процессорная шина

- Различия между традиционной архитектурой и K8/AMD64

- Оперативная память

- Разрядность шины памяти, N-канальные контроллеры памяти

- Скорость чтения и записи

- Латентность

- Процессор: сведения общего характера

- Понятие архитектуры

- Архитектура как совместимость с кодом

- Архитектура как характеристика семейства процесcоров

- 64-битные расширения классической x86 (IA32) архитектуры

- Процессорое ядро

- Различия между ядрами одной микроархитектуры

- Ревизии

- Частота работы ядра

- Особенности образования названий процессоров

- Рейтинги от AMD

- Processor Number от Intel

- Измерение скорости «в мегагерцах» — как это возможно?

- Пара слов о некоторых пикантных особенностях DDR и QDR протоколов

- Понятие архитектуры

- Процессор «крупноблочно»

- Кэш

- Общее описание и принцип действия

- Многоуровневое кэширование

- Декодер

- Исполняющие (функциональные) устройства

- Арифметико-логические устройства

- Блок вычислений с плавающей запятой

- Регистры процессора

- Кэш

- Процессор в подробностях

- Особенности кэшей

- Частота работы кэша и его шина

- Эксклюзивный и неэксклюзивный кэш

- Trace cache

- Суперскалярность и внеочередное исполнение команд

- Предварительное (опережающее) декодирование и кэширование

- Предсказание ветвлений

- Предвыборка данных

- Особенности кэшей

- Заключение

Введение

Код и данные: основной принцип работы процессора

Итак, если не пытаться изложить здесь «кратенько» курс информатики для средней школы, то единственное что хотелось бы напомнить — это то, что процессор (за редкими исключениями) исполняет не программы, написанные на каком-нибудь языке программирования (один из которых, вы, возможно, даже знаете), а некий «машинный код». То есть командами для него являются последовательности байтов, находящихся в памяти компьютера. Иногда команда может быть равна одному байту, иногда она занимает несколько байт. Там же, в основной памяти (ОЗУ, RAM) находятся и данные. Они могут находиться в отдельной области, а могут и быть «перемешаны» с кодом. Различие между кодом и данными состоит в том, что данные — это то, над чем процессор производит какие-то операции. А код — это команды, которые ему сообщают, какую именно операцию он должен произвести. Для упрощения, мы можем представить себе программу и ее данные в виде последовательности байтов некой конечной длины, располагающуюся непрерывно (не будем усложнять) в общем массиве памяти. Например, у нас есть массив памяти длиной в 1’000’000 байт, а наша программа (вместе с данными) — это байты с номерами от 1000 до 20’000. Прочие байты — это другие программы или их данные, или просто свободная память, не занятая ничем полезным.

Таким образом, «машинный код» — это команды процессора, располагающиеся в памяти. Там же располагаются данные. Для того чтобы исполнить команду, процессор должен прочитать ее из памяти. Для того чтобы произвести операцию над данными, процессор должен прочитать их из памяти, и, возможно, после произведения над ними определенного действия, записать их обратно в память в обновленном (измененном) виде. Команды и данные идентифицируются их адресом, который, по сути, представляет собой порядковый номер ячейки памяти.Общие принципы взаимодействия

процессора и ОЗУ

Возможно, кого-то удивит, что достаточно большой раздел в FAQ, посвященном x86 CPU, выделен под объяснение особенностей функционирования памяти в современных системах, основанных на данном типе процессоров. Однако факты — упрямая вещь: сами x86-процессоры ныне содержат так много блоков, отвечающих именно за оптимизацию их работы с ОЗУ, что игнорировать эту тесную связь было бы совершенно нелепо. Можно сказать даже так: уж, коль решения, связанные с оптимизацией работы с памятью, стали неотъемлемой частью самих процессоров — то и саму память можно рассматривать в качестве некоего «придатка», функционирование которого оказывает непосредственное влияние на скорость работы CPU. Без понимания особенностей взаимодействия процессора с памятью, невозможно понять, за счёт чего тот или иной процессор (та или иная система) исполняет программы медленнее или быстрее.

Контроллер памяти

Итак, ранее выше мы уже говорили о том, что как команды, так и данные, попадают в процессор из оперативной памяти. На самом деле всё немного сложнее. В большинстве современных x86-систем (то есть компьютеров на базе x86-процессоров), процессор как устройство к памяти обращаться вообще не может, так как не имеет в своем составе соответствующих узлов. Поэтому он обращается к «промежуточному» специализированному устройству, называемому контроллером памяти, а уже тот, в свою очередь — к микросхемам ОЗУ, размещенным на модулях памяти. Модули вы наверняка видели — это такие длинные узкие текстолитовые «планочки» (фактически — небольшие платы) с некоторым количеством микросхем на них, вставляемые в специальные разъемы на системной плате. Роль контроллера ОЗУ, таким образом, проста: он служит своего рода «мостом»* между памятью и использующими ее устройствами (кстати, к ним относится не только процессор, но об этом — чуть позже). Как правило, контроллер памяти входит в состав чипсета — набора микросхем, являющегося основой системной платы. От быстродействия контроллера во многом зависит скорость обмена данными между процессором и памятью, это один из важнейших компонентов, влияющих на общую производительность компьютера.

* — кстати, контроллер памяти физически находится в микросхеме чипсета, традиционно называемой «северным мостом».

Процессорная шина

Любой процессор обязательно оснащён процессорной шиной, которую в среде x86 CPU принято называть FSB (Front Side Bus). Эта шина служит каналом связи между процессором и всеми остальными устройствами в компьютере: памятью, видеокартой, жёстким диском, и так далее. Впрочем, как мы уже знаем из предыдущего раздела, между собственно памятью и процессором находится контроллер памяти. Соответственно: процессор посредством FSB связывается с контроллером памяти, а уже тот, в свою очередь, по специальной шине (назовём её, не мудрствуя лукаво, «шиной памяти») — с модулями ОЗУ на плате. Однако, повторимся: поскольку «внешняя» шина у классического x86 CPU всего одна, она используется не только для работы с памятью, но и для общения процессора со всеми остальными устройствами.

Различия между традиционной для

x86 CPU архитектурой и K8/AMD64

Революционность подхода компании AMD состоит в том, что её процессоры с архитектурой AMD64 (и микроархитектурой, которую условно принято называть «K8») оснащены множеством «внешних» шин. При этом одна или несколько шин HyperTransport служат для связи со всеми устройствами кроме памяти, а отдельная группа из одной или двух (в случае двухканального контроллера) шин — исключительно для работы процессора с памятью. Преимущество интеграции контроллера памяти прямо в процессор, очевидно: «путь от ядра до памяти» становится заметно «короче», что позволяет работать с ОЗУ быстрее. Правда, имеются у данного подхода и недостатки. Так, например, если ранее устройства типа жёсткого диска или видеокарты могли работать с памятью через выделенный, независимый контроллер — то в случае с архитектурой AMD64 они вынуждены работать с ОЗУ через контроллер, размещённый на процессоре. Так как CPU в данной архитектуре является единственным устройством, имеющим прямой доступ к памяти. Де-факто, в противостоянии «внешний контроллер vs. интегрированный», сложился паритет: с одной стороны, на данный момент AMD является единственным производителем десктопных x86-процессоров с интегрированным контроллером памяти, с другой — компания вроде бы вполне довольна этим решением, и не собирается от него отказываться. С третьей — Intel тоже не собирается отказываться от внешнего контроллера, и вполне довольна «классической схемой», проверенной годами.

Оперативная память

Разрядность шины памяти, N-канальные контроллеры памяти

По состоянию на сегодняшний день, вся память, используемая в современных десктопных x86-системах имеет шину шириной 64 бита. Это означает, что за один такт по данной шине одновременно может быть передано количество информации, кратное 8 байтам (8 байт для SDR-шин, 16 байт для DDR-шин). Особняком стоит только память типа RDRAM, применявшаяся в системах на базе процессоров Intel Pentium 4 на заре становления архитектуры NetBurst, но сейчас это направление признано тупиковым для x86-ПК (к слову — руку к этому приложила всё та же компания Intel, которая в своё время активно пропагандировала данный тип памяти). Некоторую неразбериху вносят лишь двухканальные контроллеры, обеспечивающие одновременную работу с двумя отдельными друг от друга 64-битными шинами, благодаря чему некоторые производители заявляют о некой «128-битности». Это, разумеется, чистой воды профанация. Арифметика на уровне 1-го класса в данном случае, увы, не работает: 2×64 вовсе не равно 128. Почему? Да хотя бы потому, что даже самые современные x86 CPU (см. ниже раздел FAQ «64-битные расширения классической x86 (IA32) архитектуры») не могут работать со 128-битной шиной и 128-битной адресацией. Грубо говоря: две независимые параллельно идущие дороги, шириной 2 метра каждая — могут обеспечить одновременный проезд двух автомобилей, шириной 2 метра — но никоим образом не одного, шириной 4 метра. Точно так же, N-канальный контроллер памяти может увеличить скорость работы с данными в N раз (и то больше теоретически, чем практически) — но никак не способен увеличить разрядность этих данных. Ширина шины памяти во всех современных контроллерах, применяемых в x86-системах, равна 64 битам — независимо от того, находится этот контроллер в чипсете, или в самом процессоре. Некоторые контроллеры оснащены двумя независимыми 64-битными каналами, но на разрядность шины памяти это никак не влияет — только на скорость считывания и записи информации.

Скорость чтения и записи

Скорость чтения и записи информации в память теоретически ограничивается исключительно пропускной способностью самой памяти. Так, например, двухканальный контроллер памяти стандарта DDR400 теоретически способен обеспечить скорость чтения и записи информации, равную 8 байт (ширина шины) * 2 (количество каналов) * 2 (протокол DDR, обеспечивающий передачу 2 пакетов данных за 1 такт) * 200’000’000 (фактическая частота работы шины памяти равная 200 МГц, то есть 200’000’000 тактов в секунду). Значения, получаемые в результате практических тестов, как правило, чуть ниже теоретических: сказывается «неидеальность» конструкции контроллера памяти, плюс накладки (задержки), вызванные работой подсистемы кэширования самого процессора (см. ниже раздел про процессорный кэш). Однако основной «подвох» содержится даже не в накладках, связанных с работой контроллера и подсистемы кэширования, а в том, что скорость «линейного» чтения или записи является вовсе не единственной характеристикой, влияющей на фактическую скорость работы процессора с ОЗУ. Для того чтобы понять, из каких составляющих складывается фактическая скорость работы процессора с памятью, нам необходимо кроме линейной скорости считывания или записи учитывать ещё и такую характеристику, как латентность.

Латентность

Латентность является не менее важной характеристикой с точки зрения быстродействия подсистемы памяти, чем скорость «прокачки данных», но совершенно другой, по сути. Большая скорость обмена данными хороша тогда, когда их размер относительно велик, но если нам требуется «понемногу с разных адресов» — то на первый план выходит именно латентность. Что это такое? В общем случае — время, которое требуется для того, чтобы начать считывать информацию с определённого адреса. И действительно: с момента, когда процессор посылает контроллеру памяти команду на считывание (запись), и до момента, когда эта операция осуществляется, проходит определённое количество времени. Причём оно вовсе не равно времени, которое требуется на пересылку данных. Приняв команду на чтение или запись от процессора, контроллер памяти «указывает» ей, с каким адресом он желает работать. Доступ к любому произвольно взятому адресу не может быть осуществлён мгновенно, для этого требуется определённое время. Возникает задержка: адрес указан, но память ещё не готова предоставить к нему доступ. В общем случае, эту задержку и принято называть латентностью. У разных типов памяти она разная. Так, например, память типа DDR2 имеет в среднем гораздо большие задержки, чем DDR (при одинаковой частоте передачи данных). В результате, если данные в программе расположены «хаотично» и «небольшими кусками», скорость их считывания становится намного менее важной, чем скорость доступа к «началу куска», так как задержки при переходе на очередной адрес влияют на быстродействие системы намного сильнее, чем скорость считывания или записи.

«Соревнование» между скоростью чтения (записи) и латентностью — одна из основных головных болей разработчиков современных систем: к сожалению, рост скорости чтения (записи), почти всегда приводит к увеличению латентности. Так, например, память типа SDR (PC66, PC100, PC133) обладает в среднем лучшей (меньшей) латентностью, чем DDR. В свою очередь, у DDR2 латентность ещё выше (то есть хуже), чем у DDR.

Следует понимать, что «общая» латентность подсистемы памяти зависит не только от неё самой, но и от контроллера памяти и места его расположения — все эти факторы тоже влияют на задержку. Именно поэтому компания AMD в процессе разработки архитектуры AMD64 решила «одним махом» решить проблему высокой латентности, интегрировав контроллер прямо в процессор — чтобы максимально «сократить дистанцию» между процессорным ядром и модулями ОЗУ. Затея удалась, но дорогой ценой: теперь система на базе определённого CPU архитектуры AMD64 может работать только с той памятью, на которую рассчитан его контроллер. Наверное, именно поэтому компания Intel до сих пор не решилась на такой кардинальный шаг, предпочитая действовать традиционными методами: усовершенствуя контроллер памяти в чипсете и механизм Prefetch в процессоре (про него см. ниже).

В завершение, заметим, что понятия «скорость чтения / записи» и «латентность», в общем случае, применимы к любому типу памяти — в том числе не только к классической DRAM (SDR, Rambus, DDR, DDR2), но и к кэшу (см. ниже).Процессор: сведения общего характера

Понятие архитектуры

Архитектура как совместимость с кодом

Наверняка вы часто встречались с термином «x86», или «Intel-совместимый процессор» (или «IBM PC compatible» — но это уже по отношению к компьютеру). Иногда также встречается термин «Pentium-совместимый» (почему именно Pentium — вы поймете сами чуть позже). Что за всеми этими названиями скрывается на самом деле? На данный момент наиболее корректно с точки зрения автора выглядит следующая простая формулировка: современный x86-процессор — это процессор, способный корректно исполнять машинный код архитектуры IA32 (архитектура 32-битных процессоров Intel). В первом приближении это код, исполняемый процессором i80386 (известным в народе как «386-й»), окончательно же основной набор команд IA32 сформировался с выходом процессора Intel Pentium Pro. Что означает «основной набор» и какие есть еще? Для начала ответим на первую часть вопроса. «Основной» в данном случае означает то, что с помощью исключительно этого набора команд, может быть написана любая программа, которая вообще может быть написана для процессора архитектуры x86 (или IA32, если вам так больше нравится).

Кроме того, у архитектуры IA32 существуют «официальные» расширения (дополнительные наборы команд) от разработчика самой архитектуры, компании Intel: MMX, SSE, SSE2 и SSE3. Также существуют «неофициальные» (не от Intel) расширенные наборы команд: EMMX, 3DNow! и Extended 3DNow! — их разработала компания AMD. Впрочем, «официальность» и «неофициальность» в данном случае понятие относительное — де-факто все сводится к тому, что некоторые расширения набора команд Intel как разработчик изначального набора признает, а некоторые — нет, разработчики же программного обеспечения используют то, что им лучше всего подходит. В отношении расширенных наборов команд существует одно простое правило хорошего тона: прежде чем их использовать, программа должна проверить, поддерживает ли их процессор. Иногда отступления от этого правила встречаются (и могут приводить к неправильному функционированию программ), но объективно это является проблемой некорректно написанного программного обеспечения, а не процессора.

Для чего предназначены дополнительные наборы команд? В первую очередь — для увеличения быстродействия при выполнении некоторых операций. Одна команда из дополнительного набора, как правило, выполняет действие, для которого понадобилась бы небольшая программа, состоящая из команд основного набора. Опять-таки, как правило, одна команда выполняется процессором быстрее, чем заменяющая ее последовательность. Однако в 99% случаев, ничего такого, чего нельзя было бы сделать с помощью основных команд, с помощью команд из дополнительного набора сделать нельзя.

Таким образом, упомянутая выше проверка программой поддержки дополнительных наборов команд процессором, должна выполнять очень простую функцию: если, например, процессор поддерживает SSE — значит, считать будем быстро и с помощью команд из набора SSE. Если нет — будем считать медленнее, с помощью команд из основного набора. Корректно написанная программа обязана действовать именно так. Впрочем, сейчас практически никто не проверяет у процессора наличие поддержки MMX, так как все CPU, вышедшие за последние 5 лет, этот набор поддерживают гарантированно. Для справки приведем табличку, на которой обобщена информация о поддержке различных расширенных наборов команд различными десктопными (предназначенными для настольных ПК) процессорами.

| Процессор | MMX | EMMX | 3DNow! | SSE | E3DNow! | SSE2 | SSE3 |

| Intel Pentium II | + | — | — | — | — | — | — |

| Intel Celeron до 533 MHz | + | — | — | — | — | — | — |

| Intel Pentium III | + | — | — | + | — | — | — |

| Intel Celeron 533—1400 MHz | + | — | — | + | — | — | — |

| Intel Pentium 4 | + | — | — | + | — | + | +/—* |

| Intel Celeron от 1700 MHz | + | — | — | + | — | + | — |

| Intel Celeron D | + | — | — | + | — | + | + |

| Intel Pentium 4 eXtreme Edition | + | — | — | + | — | + | +/—* |

| Intel Pentium eXtreme Edition | + | — | — | + | — | + | + |

| Intel Pentium D | + | — | — | + | — | + | + |

| AMD K6 | + | + | — | — | — | — | — |

| AMD K6-2 | + | + | + | — | — | — | — |

| AMD K6-III | + | + | + | — | — | — | — |

| AMD Athlon | + | + | + | — | + | — | — |

| AMD Duron до 900 MHz | + | + | + | — | + | — | — |

| AMD Athlon XP | + | + | + | + | + | — | — |

| AMD Duron от 1000 MHz | + | + | + | + | + | — | — |

| AMD Athlon 64 / Athlon FX | + | + | + | + | + | + | +/—* |

| AMD Sempron | + | + | + | + | + | +/—* | +/—* |

| AMD Athlon 64 X2 | + | + | + | + | + | + | + |

| VIA C3 | + | + | +/—* | +/—* | — | — | — |

* в зависимости от модификации

На данный момент всё популярное десктопное программное обеспечение (операционные системы Windows и Linux, офисные пакеты, компьютерные игры, и прочее) разрабатывается именно для x86-процессоров. Оно выполняется (за исключением «дурно воспитанных» программ) на любом x86-процессоре, независимо от того, кто его произвел. Поэтому вместо ориентированных на разработчика изначальной архитектуры терминов «Intel-совместимый» или «Pentium-совместимый», стали употреблять нейтральное название: «x86-совместимый процессор», «процессор с архитектурой x86». В данном случае под «архитектурой» понимается совместимость с определённым набором команд, то есть, можно сказать, «архитектура процессора с точки зрения программиста». Есть и другая трактовка того же термина.

Архитектура как характеристика семейства процесcоров

«Железячники» — люди, работающие в основном не с программным обеспечением, а с аппаратным, под «архитектурой» понимают несколько другое (правда, более корректно то, что они называют «архитектурой», называется «микроархитектурой», но де-факто приставку «микро» частенько опускают). Для них «архитектура CPU» — это некий набор свойств, присущий целому семейству процессоров, как правило, выпускаемому в течение многих лет (иначе говоря — «внутренняя конструкция», «организация» этих процессоров). Так, например, любой специалист по x86 CPU вам скажет, что процессор с ALU, работающими на удвоенной частоте, QDR-шиной, Trace cache, и, возможно, поддержкой технологии Hyper-Threading — это «процессор архитектуры NetBurst» (не пугайтесь незнакомых терминов — все они будут разъяснены чуть позже). А процессоры Intel Pentium Pro, Pentium II и Pentium III — это «архитектура P6». Таким образом, понятие «архитектуры» применительно к процессорам несколько двойственно: под ним может пониматься как совместимость с неким единым набором команд, так и совокупность аппаратных решений, присущих определённой достаточно широкой группе процессоров. Разумеется, такой дуализм одного из основополагающих понятий не очень удобен, однако так уж сложилось, и вряд ли в ближайшее время что-то поменяется…

64-битные расширения классической x86 (IA32) архитектуры

Не так давно оба ведущих производителя x86 CPU анонсировали две практически идентичных* технологии (впрочем, AMD предпочитает называть это архитектурой), благодаря которым классические x86 (IA32) CPU получили статус 64-битных. В случае с AMD данная технология получила наименование «AMD64» (64-битная архитектура AMD), в случае с Intel — «EM64T» (расширенная 64-битная технология работы с памятью). Также почтенные аксакалы, знакомые с историей вопроса, иногда употребляют наименование «x86-64» — как общее обозначение всех 64-битных расширений архитектуры x86, не привязанное к зарегистрированным торговым маркам какого-либо производителя. Де-факто, употребление одного из трёх, приведенных выше, наименований, зависит больше от личных предпочтений употребляющего, чем от фактических различий — ибо различия между AMD64 и EM64T умещаются на кончике очень тонкой иглы. К тому же, сама AMD ввела «фирменное» наименование «AMD64» лишь незадолго до анонса собственных процессоров на основе данной архитектуры, а до этого совершенно спокойно употребляла в собственных документах более нейтральное «x86-64». Однако так или иначе, всё сводится к одному: некоторые внутренние регистры процессоров стали вместо 32-битных 64-битными, 32-битные команды x86-кода получили свои 64-битные аналоги, кроме того, объём адресуемой памяти (включая не только физическую, но и виртуальную) многократно увеличился (за счёт того, что адрес приобрёл вместо 32-битного 64-битный формат). Количество маркетинговых спекуляций на тему «64-битности» превысило все разумные пределы, поэтому нам следует рассмотреть достоинства данного нововведения особенно пристально. Итак: что же на самом деле изменилось, а что — нет?

* — Доводы о том, что Intel, дескать, «нагло скопировала EM64T с AMD64» не выдерживают никакой критики. И вовсе не потому, что это не так — а потому, что вовсе не «нагло». Есть такое понятие: «кросс-лицензионное соглашение». Если таковое соглашение имеет место быть, это означает, что все разработки одной компании в определённой области, становятся автоматически доступными другой, равно как и разработки другой автоматически становятся доступны первой. Intel воспользовалась кросс-лицензированием для разработки EM64T, взяв за основу AMD64 (чего никто никогда не отрицал). AMD воспользовалась тем же соглашением для введения в свои процессоры поддержки наборов дополнительных инструкций SSE2 и SSE3, разработанных Intel. И ничего в этом постыдного нет: раз договорились «делиться» разработками — значит, надо делиться.

Что не изменилось? В первую очередь — быстродействие процессоров. Вопиющей глупостью будет считать, что один и тот же процессор при переходе из привычного 32-битного в 64-битный режим (а 32-битный режим все нынешние x86 CPU поддерживают в обязательном порядке) станет работать в 2 раза быстрее. Разумеется, в некоторых случаях некое ускорение от использования 64-битной целочисленной арифметики может присутствовать — но количество этих случаев сильно ограничено, и большинства современного пользовательского программного обеспечения они никак не касаются. Кстати: а почему мы употребили термин «64-битная целочисленная арифметика»? А потому, что блоки операций с плавающей точкой (см. ниже) во всех x86-процессорах уже давным-давно не 32-битные. И даже не 64-битные. Классический x87 FPU (см. ниже), окончательно ставший частью CPU ещё во времена старого доброго 32-битного Intel Pentium — уже был 80-битным. Операнды команд SSE и SSE2/3 — и вовсе 128-битные! В этом плане архитектура x86 достаточно парадоксальна: при всём притом, что формально процессоры данной архитектуры достаточно долгое время оставались 32-битными — разрядность тех блоков, где «большая битность» была реально необходима — наращивалась совершенно независимо от остальных. Например, процессоры AMD Athlon XP и Intel Pentium 4 «Northwood» совмещали в себе блоки, работающие с 32-битными, 80-битными, и 128-битными операндами. 32-битными оставались лишь основной набор команд (унаследованный от первого процессора архитектуры IA32 — Intel 386) и адресация памяти (максимум 4 гигабайта, если не считать «извращений» типа Intel PAE).

Таким образом, то, что процессоры AMD и Intel стали «формально 64-битными», на практике принесло нам лишь три усовершенствования: появление команд для работы с 64-битными целыми числами, увеличение количества и/или разрядности регистров, и увеличение максимального объёма адресуемой памяти. Заметим: реальной пользы этих нововведений (особенно третьего!) никто не отрицает. Равно как никто не отрицает заслуг компании AMD в продвижении идеи «осовременивания» (за счёт введения 64-битности) x86-процессоров. Мы лишь хотим предостеречь от чрезмерных ожиданий: не стоит надеяться на то, что компьютер, покупавшийся «в ценовом классе ВАЗа», от установки 64-битного программного обеспечения станет «лихим Мерседесом». Чудес на свете не бывает…

Процессорное ядро

Различия между ядрами одной микроархитектуры

«Процессорное ядро» (как правило, для краткости его называют просто «ядро») — это конкретное воплощение [микро]архитектуры (т.е. «архитектуры в аппаратном смысле этого слова»), являющееся стандартом для целой серии процессоров. Например, NetBurst — это микроархитектура, которая лежит в основе многих сегодняшних процессоров Intel: Celeron, Pentium 4, Xeon. Микроархитектура задает общие принципы: длинный конвейер, использование определенной разновидности кэша кода первого уровня (Trace cache), прочие «глобальные» особенности. Ядро — более конкретное воплощение. Например, процессоры микроархитектуры NetBurst с шиной 400 МГц, кэшем второго уровня 256 килобайт, и без поддержки Hyper-Threading — это более-менее полное описание ядра Willamette. А вот ядро Northwood имеет кэш второго уровня уже 512 килобайт, хотя также основано на NetBurst. Ядро AMD Thunderbird основано на микроархитектуре K7, но не поддерживает набор команд SSE, а вот ядро Palomino — уже поддерживает.

Таким образом, можно сказать что «ядро» – это конкретное воплощение определенной микроархитектуры «в кремнии», обладающее (в отличие от самой микроархитектуры) определенным набором строго обусловленных характеристик. Микроархитектура — аморфна, она описывает общие принципы построения процессора. Ядро — конкретно, это микроархитектура, «обросшая» всевозможными параметрами и характеристиками. Чрезвычайно редки случаи, когда процессоры сменяли микроархитектуру, сохраняя название. И, наоборот, практически любое наименование процессора хотя бы несколько раз за время своего существования «меняло» ядро. Например, общее название серии процессоров AMD — «Athlon XP» — это одна микроархитектура (K7), но целых четыре ядра (Palomino, Thoroughbred, Barton, Thorton). Разные ядра, построенные на одной микроархитектуре, могут иметь, в том числе разное быстродействие.

Ревизии

Ревизия — одна из модификаций ядра, крайне незначительно отличающаяся от предыдущей, почему и не заслуживает звания «нового ядра». Как правило, из выпусков очередной ревизии производители процессоров не делают большого события, это происходит «в рабочем порядке». Так что даже если вы покупаете один и тот же процессор, с полностью аналогичным названием и характеристиками, но с интервалом где-то в полгода — вполне возможно, фактически он будет уже немного другой. Выпуск новой ревизии, как правило, связан с какими-то мелкими усовершенствованиями. Например, удалось чуть-чуть снизить энергопотребление, или понизить напряжение питания, или еще что-то оптимизировать, или была устранена пара мелких ошибок. С точки зрения производительности мы не помним ни одного примера, когда бы одна ревизия ядра отличалась от другой настолько существенно, чтобы об этом имело смысл говорить. Хотя чисто теоретически возможен и такой вариант — например, подвергся оптимизации один из блоков процессора, ответственный за исполнение нескольких команд. Подводя итог, можно сказать что «заморачиваться» ревизиями процессоров чаще всего не стоит: в очень редких случаях изменение ревизии вносит какие-то кардинальные изменения в процессор. Достаточно просто знать, что есть такая штука — исключительно для общего развития.

Частота работы ядра

Как правило, именно этот параметр в просторечии именуют «частотой процессора». Хотя в общем случае определение «частота работы ядра» всё же более корректно, так как совершенно не обязательно все составляющие CPU функционируют на той же частоте, что и ядро (наиболее частым примером обратного являлись старые «слотовые» x86 CPU — Intel Pentium II и Pentium III для Slot 1, AMD Athlon для Slot A — у них L2-кэш функционировал на 1/2, и даже иногда на 1/3 частоты работы ядра). Ещё одним распространённым заблуждением является уверенность в том, что частота работы ядра однозначным образом определяет производительность. На самом деле это дважды не так: во-первых, каждое конкретное процессорное ядро (в зависимости от того, как оно спроектировано, сколько содержит исполняющих блоков различных типов, и т.д. и т.п.) может исполнять различное количество команд за один такт, частота же — это всего лишь количество таких тактов в секунду. Таким образом (приведенное далее сравнение, разумеется, очень сильно упрощено и поэтому весьма условно) процессор, ядро которого исполняет 3 инструкции за такт, может иметь на треть меньшую частоту, чем процессор, исполняющий 2 инструкции за такт — и при этом обладать полностью аналогичным быстродействием.

Во-вторых, даже в рамках одного и того же ядра, увеличение частоты вовсе не всегда приводит к пропорциональному увеличению быстродействия. Здесь вам очень пригодятся знания, которые вы могли почерпнуть из раздела «Общие принципы взаимодействия процессора и ОЗУ». Дело в том, что скорость исполнения команд ядром процессора — это вовсе не единственный показатель, влияющий на скорость выполнения программы. Не менее важна скорость поступления команд и данных на CPU. Представим себе чисто теоретически такую систему: быстродействие процессора — 10’000 команд в секунду, скорость работы памяти — 1000 байт в секунду. Вопрос: даже если принять, что одна команда занимает не более одного байта, а данных у нас нет совсем, с какой скоростью будет исполняться программа в такой системе? Правильно: не более 1000 команд в секунду, и производительность CPU тут совершенно ни при чём: мы будем ограничены не ей, а скоростью поступления команд в процессор. Таким образом, следует понимать: невозможно непрерывно наращивать одну только частоту ядра, не ускоряя одновременно подсистему памяти, так как в этом случае начиная с определённого этапа, увеличение частоты CPU перестанет сказываться на увеличении быстродействия системы в целом.

Особенности образования названий процессоров

Раньше, когда небо было голубее, пиво — вкуснее, а девушки — красивее, процессоры называли просто: имя производителя + название модельного ряда + частота. Например: «AMD K6-2 450 MHz». В настоящее время уже оба основных производителя от этой традиции отошли, и вместо частоты употребляют какие-то непонятные циферки, обозначающие невесть что. Краткому объяснению того, что же на самом деле эти циферки обозначают, и посвящены следующие два раздела.

Рейтинги от AMD

Причина, по которой компания AMD «изъяла» частоту из наименования своих процессоров, и заменила её некой абстрактной цифрой — общеизвестна: после появления процессора Intel Pentium 4, который работает на очень высоких частотах, процессоры AMD рядом с ним стали «плохо выглядеть на витрине» — покупатель не верил, что CPU с частотой, например, 1500 МГц, может обогнать CPU с частотой 2000 МГц. Поэтому частоту в наименовании заменили рейтингом. Формальная («де-юре», так сказать) трактовка этого рейтинга в устах AMD в разные времена звучала немного по-разному, но ни разу не прозвучала в том виде, в каком её воспринимали пользователи: процессор AMD с неким рейтингом, должен быть как минимум не медленнее процессора Intel Pentium 4 с соответствующей данному рейтингу частотой. Между тем, ни для кого не являлось особенным секретом, что именно такая трактовка и являлась конечной целью введения рейтинга. В общем, все всё прекрасно понимали, но AMD старательно делала вид, что она тут ни при чём :). Пенять ей за это не стоит: в конкурентной борьбе применяются совсем другие правила, чем в рыцарских поединках. Тем более что результаты независимых тестов демонстрировали: в целом, рейтинги своим процессорам AMD назначает достаточно справедливые. Собственно, именно до тех пор, пока это так — вряд ли имеет смысл протестовать против использования рейтинга. Правда, остаётся открытым один вопрос: а к чему же (нас интересует, понятное дело, состояние де-факто, а не разъяснения маркетингового отдела) будет привязан рейтинг процессоров AMD чуть позже, когда вместо Pentium 4 Intel начнёт выпускать какой-нибудь другой процессор?

Processor Number от Intel

Что нужно запомнить сразу: Processor Number (далее PN) у процессоров Intel — это не рейтинг. Не рейтинг производительности, и не рейтинг чего-либо другого. Фактически, это просто «артикул», элемент строчки в складской ведомости, единственная задача которого — сделать так, чтобы строчка, обозначающая один процессор, отличалась от строчки, обозначающей другой. В рамках серии (первая цифра PN), две остальные цифры, в принципе, кое о чём могут сказать, но, учитывая наличие таблиц, в которых приведено полное соответствие между PN и реальными параметрами, мы не видим особого смысла в том, чтобы заучивать какие-то промежуточные соответствия. Мотивация, которой руководствовалась Intel, вводя PN (вместо опять-таки указания частоты CPU) — более сложная, чем у AMD. Необходимость введения PN (как её объясняет сама Intel) связана, прежде всего, с тем, что два основных конкурента по-разному подходят к вопросу об уникальности наименования CPU. Например, у AMD название «Athlon 64 3200+» может обозначать сразу четыре процессора с несколько различными техническими характеристиками (но одинаковым «рейтингом»). Intel придерживается мнения, что наименование процессора должно быть уникальным, в связи с чем ранее компании приходилось «изворачиваться», добавляя к значению частоты в наименовании различные буквы, и это приводило к путанице. По идее, PN должен был эту путаницу устранить. Трудно сказать, была ли достигнута поставленная цель: всё равно номенклатура процессоров Intel осталась достаточно сложной. С другой стороны, это неизбежно, так как ассортимент продуктов уж больно велик. Однако независимо от всего прочего, одного эффекта де-факто добиться точно удалось: теперь только разбирающиеся в вопросе специалисты могут по названию процессора быстро и точно «по памяти» сказать, что он собой представляет, и какова будет его производительность в сравнении с другими CPU. Насколько это хорошо? Сложно сказать. Мы предпочтём воздержаться от комментариев.

Измерение скорости «в мегагерцах» — как это возможно?

Никак это невозможно, потому что скорость не измеряется в мегагерцах, как не измеряется расстояние в килограммах. Однако господа маркетологи давно уже поняли, что в словесном поединке между физиком и психологом побеждает всегда последний — причём независимо от того, кто на самом деле прав. Поэтому мы и читаем про «сверхбыструю 1066 MHz FSB», мучительно пытаясь понять, как скорость может измеряться с помощью частоты. На самом деле, раз уж прижилась такая извращённая тенденция, нужно просто чётко представлять себе, что имеется в виду. А имеется в виду следующее: если мы «закрепим» ширину шины на N битах — то её пропускная способность действительно будет зависеть от того, на какой частоте данная шина функционирует, и какое количество данных она способна передавать за такт. По обычной процессорной шине с «одинарной» скоростью (такая шина была, например, у процессора Intel Pentium III) за такт передаётся 64 бита, то есть 8 байт. Соответственно, если рабочая частота шины равна 100 МГц (100’000’000 тактов в секунду) — то скорость передачи данных будет равна 8 байт * 100’000’000 герц ~= 763 мегабайта в секунду (а если считать в «десятичных мегабайтах», в которых принято считать потоки данных, то ещё красивее — 800 мегабайт в секунду). Соответственно, если на тех же 100 мегагерцах работает DDR-шина, способная передавать за один такт удвоенный объём данных — скорость вырастет ровно вдвое. Поэтому, согласно парадоксальной логике господ маркетологов, данную шину следует именовать «200-мегагерцевой». А если это ещё и QDR (Quad Data Rate) шина — то она и вовсе «400-мегагерцевая» получается, так как за один такт передаёт четыре пакета данных. Хотя реальная частота работы у всех трёх вышеописанных шин одинаковая — 100 мегагерц. Вот так «мегагерцы» и стали синонимом скорости.

Таким образом, QDR-шина (с «учетверённой» скоростью), работающая на реальной частоте 266 мегагерц, волшебным образом оказывается у нас «1066-мегагерцевой». Цифра «1066» в данном случае олицетворяет то, что её пропускная способность ровно в 4 раза больше «односкоростной» шины, работающей на той же самой частоте. Вы ещё не запутались?.. Привыкайте! Это вам не какая-нибудь теория относительности, тут всё намного сложней и запущенней… Впрочем, самое главное здесь — выучить наизусть один простой принцип: если уж мы занимаемся таким извращением, как сравнение скорости двух шин между собой «в мегагерцах» — то они обязательно должны быть одинаковой ширины. Иначе получается как в одном форуме, где человек всерьёз доказывал, что пропускная способность AGP2X («133-мегагерцевая», но 32-битная шина) — выше, чем пропускная способность FSB у Pentium III 800 (реальная частота 100 МГц, ширина 64 бита).

Пара слов о некоторых пикантных особенностях DDR и QDR протоколов

Как уже было сказано выше, в режиме DDR по шине за один такт передаётся удвоенный объём информации, а в режиме QDR — учетверённый. Правда, в документах, ориентированных больше на прославление достижений производителей, чем на объективное освещение реалий, почему-то всегда забывают указать одно маленькое «но»: режимы удвоенной и учетверённой скорости включаются только при пакетной передаче данных. То есть, если мы запросили из памяти парочку мегабайтов с адреса X по адрес Y — то да, эти два мегабайта будут переданы с удвоенной/учетверённой скоростью. А вот сам запрос на данные посылается по шине с «одинарной» скоростью — всегда! Соответственно, если запросов у нас много, а размер пересылаемых данных не очень велик, то количество данных, которые «путешествуют» по шине с одинарной скоростью (а запрос — это тоже данные) будет почти равно количеству тех, которые передаются со скоростью удвоенной или учетверённой. Вроде бы нам никто открыто не врал, вроде бы DDR и QDR действительно работают, но… как говорится в одном старом анекдоте: «то ли он у кого-то украл шубу, то ли у него кто-то украл шубу, но что-то там с шубой не то…» ;)Процессор «крупноблочно»

Кэш

Общее описание и принцип действия

Во всех современных процессорах есть кэш (по-английски — cache). Кэш — это некая особенная разновидность памяти (основная особенность, кардинально отличающая кэш от ОЗУ — скорость работы), которая является своего рода «буфером» между контроллером памяти и процессором. Служит этот буфер для увеличения скорости работы с ОЗУ. Каким образом? Сейчас попытаемся объяснить. При этом мы решили отказаться от попахивающих детским садом сравнений, которые частенько встречаются в популяризаторской литературе на процессорную тематику (бассейны, соединённые трубами разного диаметра, и т.д. и т.п.). Всё-таки человек, который дочитал статью до этого места, и не заснул — наверное, способен выдержать и «переварить» чисто техническое объяснение, без бассейнов, кошечек и одуванчиков.

Итак, представим, что у нас есть много сравнительно медленной памяти (пусть это будет ОЗУ размером 10’000’000 байт) и относительно мало очень быстрой (пусть это будет кэш размером всего 1024 байта). Как нам с помощью этого несчастного килобайта увеличить скорость работы со всей памятью вообще? А вот здесь следует вспомнить, что данные в процессе работы программы, как правило, не бездумно перекидываются с места на место — они изменяются. Считали из памяти значение какой-то переменной, прибавили к нему какое-то число — записали обратно на то же место. Считали массив, отсортировали по возрастанию — опять-таки записали в память. То есть в один какой-то момент программа работает не со всей памятью целиком, а, как правило, с относительно маленьким её фрагментом. Какое решение напрашивается? Правильно: загрузить этот фрагмент в «быструю» память, обработать его там, а потом уже записать обратно в «медленную» (или просто удалить из кэша, если данные не изменялись). В общем случае, именно так и работает процессорный кэш: любая считываемая из памяти информация попадает не только в процессор, но и в кэш. И если эта же информация (тот же адрес в памяти) нужна снова, сначала процессор проверяет: а нет ли её в кэше? Если есть — информация берётся оттуда, и обращения к памяти не происходит вовсе. Аналогично с записью: информация, если её объём влезает в кэш — пишется именно туда, и только потом, когда процессор закончил операцию записи, и занялся выполнением других команд, данные, записанные в кэш, параллельно с работой процессорного ядра «потихоньку выгружаются» в ОЗУ.

Разумеется, объём данных, прочитанных и записанных за всё время работы программы — намного больше объёма кэша. Поэтому некоторые из них приходится время от времени удалять, чтобы в кэш могли поместиться новые, более актуальные. Самый простой из известных механизмов обеспечения данного процесса — отслеживание времени последнего обращения к данным, находящимся в кэше. Так, если нам необходимо поместить новые данные в кэш, а он уже «забит под завязку», контроллер, управляющий кэшем, смотрит: к какому фрагменту кэша не происходило обращения дольше всего? Именно этот фрагмент и является первым кандидатом на «вылет», а на его место записываются новые данные, с которыми нужно работать сейчас. Вот так, в общих чертах, работает механизм кэширования в процессорах. Разумеется, приведенное выше объяснение весьма примитивно, на самом деле всё ещё сложнее, но, надеемся, общее представление о том, зачем процессору нужен кэш и как он работает, вы получить смогли.

А для того чтобы было понятно, насколько важен кэш, приведем простой пример: скорость обмена данными процессора Pentium 4 со своим кэшам более чем в 10 раз (!) превосходит скорость его работы с памятью. Фактически, в полную силу современные процессоры способны работать только с кэшем: как только они сталкиваются с необходимостью прочитать данные из памяти — все их хваленые мегагерцы начинают просто «греть воздух». Опять-таки, простой пример: выполнение простейшей инструкции процессором происходит за один такт, то есть за секунду он может выполнить такое количество простых инструкций, какова его частота (на самом деле еще больше, но это оставим на потом…). А вот время ожидания данных из памяти может в худшем случае составить более 200 тактов! Что делает процессор, пока он ждет нужных данных? А ничего он не делает. Просто стоит и ждет…

Многоуровневое кэширование

Специфика конструирования современных процессорных ядер привела к тому, что систему кэширования в подавляющем большинстве CPU приходится делать многоуровневой. Кэш первого уровня (самый «близкий» к ядру) традиционно разделяется на две (как правило, равные) половины: кэш инструкций (L1I) и кэш данных (L1D). Это разделение предусматривается так называемой «гарвардской архитектурой» процессора, которая по состоянию на сегодня является самой популярной теоретической разработкой для построения современных CPU. В L1I, соответственно, аккумулируются только команды (с ним работает декодер, см. ниже), а в L1D — только данные (они впоследствии, как правило, попадают во внутренние регистры процессора). «Над L1» стоит кэш второго уровня — L2. Он, как правило, больше по объёму, и является уже «смешанным» — там располагаются и команды, и данные. L3 (кэш третьего уровня), как правило, полностью повторяет структуру L2, и в современных x86 CPU встречается редко. Чаще всего, L3 — это плод компромисса: за счёт использование более медленной и узкой шины, его можно сделать очень большим, но при этом скорость L3 всё равно остаётся более высокой, чем скорость памяти (хотя и не такой высокой, как у L2-кэша). Тем не менее, алгоритм работы с многоуровневым кэшем в общих чертах не отличается от алгоритма работы с одноуровневым, просто добавляются лишние итерации: сначала информация ищется в L1, если её там нет — в L2, потом — в L3, и уже потом, если ни на одном уровне кэша она не найдена — идёт обращение к основной памяти (ОЗУ).

Декодер

На самом деле, исполнительные блоки всех современных десктопных x86-процессоров… вовсе не работают с кодом в стандарте x86. У каждого процессора есть своя, «внутренняя» система команд, не имеющая ничего общего с теми командами (тем самым «кодом»), которые поступают извне. В общем случае, команды, исполняемые ядром — намного проще, «примитивнее», чем команды стандарта x86. Именно для того, чтобы процессор «внешне выглядел» как x86 CPU, и существует такой блок как декодер: он отвечает за преобразование «внешнего» x86-кода во «внутренние» команды, исполняемые ядром (при этом достаточно часто одна команда x86-кода преобразуется в несколько более простых «внутренних»). Декодер является очень важной частью современного процессора: от его быстродействия зависит то, насколько постоянным будет поток команд, поступающих на исполняющие блоки. Ведь они неспособны работать с кодом x86, поэтому то, будут они что-то делать, или простаивать — во многом зависит от скорости работы декодера. Достаточно необычный способ ускорить процесс декодирования команд реализовала в процессорах архитектуры NetBurst компания Intel — см. ниже про Trace cache.

Исполняющие (функциональные) устройства

Пройдя через все уровни кэша и декодер, команды наконец-то попадают на те блоки, ради которых вся эта катавасия и устраивалась: исполняющие устройства. По сути, именно исполняющие устройства и являются единственно необходимым элементом процессора. Можно обойтись без кэша — скорость снизится, но программы работать будут. Можно обойтись без декодера — исполняющие устройства станут сложнее, но работать процессор будет. В конце концов, ранние процессоры архитектуры x86 (i8086, i80186, 286, 386, 486, Am5x86) — как-то без декодера обходились. Без исполняющих устройств обойтись невозможно, ибо именно они исполняют код программы. В самом первом приближении они традиционно делятся на две больших группы: арифметико-логические устройства (ALU) и блок вычислений с плавающей точкой (FPU).

Арифметико-логические устройства

ALU традиционно отвечают за два типа операций: арифметические действия (сложение, вычитание, умножение, деление) с целыми числами, логические операции с опять-таки целыми числами (логическое «и», логическое «или», «исключающее или», и тому подобные). Что, собственно, и следует из их названия. Блоков ALU в современных процессорах, как правило, несколько. Для чего — вы поймёте позже, прочитав раздел «Суперскалярность и внеочередное исполнение команд». Понятно, что ALU может исполнить только те команды, которые предназначены для него. Распределением команд, поступающих с декодера, по различным исполняющим устройствам, занимается специальный блок, но это уже, как говорится, «слишком сложные материи», и их вряд ли имеет смысл разъяснять в материале, который посвящен лишь поверхностному ознакомлению с основными принципами работы современных x86 CPU.

Блок вычислений с плавающей запятой*

FPU занимается выполнением команд, работающих с числами с плавающей запятой, кроме того, традиционно на него «вешают всех собак» в виде всяческих дополнительных наборов команд (MMX, 3DNow!, SSE, SSE2, SSE3…) — независимо от того, работают они с числами с плавающей запятой, или с целыми. Как и в случае с ALU, отдельных блоков в FPU может быть несколько, и они способны работать параллельно.

* — согласно традиций русской математической школы, мы называем FPU «блоком вычислений с плавающей запятой», хотя буквально его название (Floating Point Unit) переводится как «…с плавающей точкой» — согласно американскому стандарту написания таких чисел.

Регистры процессора

Регистры — по сути, те же ячейки памяти, но «территориально» они расположены прямо в процессорном ядре. Разумеется, скорость работы с регистрами во много раз превосходит как скорость работы с ячейками памяти, расположенными в основном ОЗУ (тут вообще на порядки…), так и с кэшами любого уровня. Поэтому большинство команд архитектуры x86 предусматривают осуществление действий именно над содержимым регистров, а не над содержимым памяти. Однако общий объём регистров процессора, как правило, очень мал — он не сравним даже с объёмом кэшей первого уровня. Поэтому де-факто код программы (не на языке высокого уровня, а именно бинарный, «машинный») часто содержит следующую последовательность операций: загрузить в один из регистров процессора информацию из ОЗУ, загрузить в другой регистр другую информацию (тоже из ОЗУ), произвести некое действие над содержимым этих регистров, поместив результат в третий — а потом снова выгрузить результат из регистра в основную память. Процессор в подробностях

Особенности кэшей

Частота работы кэша и его шина